### INSTITUTO POLITÉCNICO NACIONAL

# ESCUELA SUPERIOR DE INGENIERÍA MECÁNICA Y ELÉCTRICA

#### UNIDAD PROFESIONAL CULHUACAN

### "TÉCNICAS DE MODULACIÓN DE VECTOR DE ESPACIO Y SINCRONIZACIÓN PARA CONVERTIDORES ELECTRÓNICOS DE ENERGÍA"

#### **TESIS**

QUE PARA OBTENER EL TÍTULO DE INGENIERO EN COMUNICACIONES Y ELECTRÓNICA PRESENTA:

**KEVIN CANO PULIDO**

ASESORES:

Dr. ISMAEL ARAUJO VARGAS

Ing. ALEJANDRO TAPIA HERNÁNDEZ

OCTUBRE 2013

#### INSTITUTO POLITÉCNICO NACIONAL ESCUELA SUPERIOR DE INGENIERÍA MECÁNICA Y ELÉCTRICA UNIDAD CULHUACAN

#### **TESIS INDIVIDUAL**

Que como prueba escrita de su Examen Profesional para obtener el Título de Ingeniero en Comunicaciones y Electrónica, deberán desarrollar el C:

#### **KEVIN CANO PULIDO**

### "TECNICAS DE MODULACION DE VECTOR DE ESPACIO Y SINCRONIZACION PARA CONVERTIDORES ELECTRONICOS DE ENERGIA"

En esta tesis se muestra el análisis, diseño y construcción de un PLL para un convertidor inversor controlado con Modulación de vector de espacio. Describe la manera en la que se controla un inversor trifásico tradicional con esta modulación y se desarrolla un programa que se implementa en un microcontrolador. Además, se hace un recuento de las principales herramientas para sincronizar circuitos. De esta manera se explica el funcionamiento de un PLL y se desarrolla uno mismo de manera digital implementándose en un microcontrolador. Finalmente se muestran los resultados obtenidos de manera simulada y experimental. Este último apartado demuestra el correcto funcionamiento del PLL.

#### **CAPITULADO**

CAPITULO 1 ESTADO DE ARTE

CAPITULO 2 MODULACION DE VECTOR DE ESPACIO DE ANCHO DE PULSO

CAPITULO 3 SINCRONIZADOR DE FASE CERRADA

CAPITULO 4 IMPLEMENTACION DIGITAL

CAPITULO 5 PRUEBAS Y RESULTADOS

CAPITULO 6 OBSERVACIONES Y CONCLUSIONES

ANEXO A CODIGO DEL PROGRAMA DEL SVPWM Y EL PLL DIGITAL

México D. F., a 19 de agosto del 2013

PRIMER ASESOR:

**SEGUNDO ASESOR:**

ING. ISMAEL ARAUJO VARGAS

ING. ALEJANDRO TAPIA HERNANDEZ

Vo. Bo.

**APROBADO**

M. en C. ANTONIO ROMERO ROJANO

JEFE DE LA CARRERA DE I.C.E.

M. en C. HECTOR BECERRIL MENDOZA

SUBDIRECTOR ACADÉMICO

### **Índice General**

| Índice General                                                                                 |              |

|------------------------------------------------------------------------------------------------|--------------|

| Índice de Figuras                                                                              | V            |

| Índice de Tablas                                                                               | VI           |

| AGRADECIMIENTOS                                                                                | VII          |

| DEDICATORIA                                                                                    | IX           |

| RESUMEN                                                                                        |              |

| CAPÍTULO 1                                                                                     | 1            |

| 1. Estado del Arte                                                                             | 1            |

| 1.1. Introducción                                                                              | 1            |

| 1.2. Estado del arte relativo a Convertidores electrónicos de energía que op suministro de CA. |              |

| 1.2.1. Rectificadores                                                                          | 2            |

| 1.2.1.1. Rectificadores naturalmente controlados                                               | 2            |

| 1.2.1.2. Rectificadores controlados                                                            | 3            |

| 1.2.1.3. Rectificadores activos                                                                | 3            |

| 1.2.1.4. Resumen                                                                               | Z            |

| 1.2.2. Ciclo-convertidores                                                                     | Z            |

| 1.2.2.1. Ciclo-convertidores a base de inversores                                              | Z            |

| 1.2.2.2. Ciclo-convertidores en base a tiristores                                              | 5            |

| 1.2.2.3. Convertidores Matriciales                                                             | 6            |

| 1.2.2.4. Resumen                                                                               | 6            |

| 1.2.3. Inversores.                                                                             | 7            |

| 1.2.3.1. Inversores.                                                                           | 7            |

| 1.2.3.2. Resumen                                                                               | <del>7</del> |

| 1.2.4. Filtros Activos.                                                                        | 8            |

| 1.2.4.1. Esquema General.                                                                      | 8            |

| 1.2.4.2. Clasificación                                                                         | 8            |

| 1.2.4.3. Resumen                                                                               | 8            |

| 1.3. Estado del arte relativo a Técnicas de sincronización de circuitos                        | <u>C</u>     |

| 1.3.1. Detectores de cruce por cero                                                            | c            |

| 1.3.2          | El PLL                                                                      | 10 |

|----------------|-----------------------------------------------------------------------------|----|

| 1.3.2          | .1. Detector de Fase                                                        | 10 |

| 1.3.2          | .2. EL VCO                                                                  | 13 |

| 1.3.2          | 3. Compensador                                                              | 14 |

| 1.3.3<br>de er | Herramientas modernas para manipular y procesar señales trifásicas en conv  |    |

| 1.3.3          | .1. Transformación de Clarke                                                | 14 |

| 1.3.3          | .2. Transformación de Park                                                  | 16 |

| 1.4.           | Resumen del estado del arte.                                                | 16 |

| 1.5.           | Objetivo                                                                    | 16 |

| 1.6.           | Bosquejo                                                                    | 17 |

| 1.7.           | Referencias                                                                 | 18 |

| CAPÍTU         | JLO 2                                                                       | 19 |

| 2. M           | odulación de vector de espacio de ancho de pulso                            | 19 |

| 2.1.           | Introducción                                                                | 19 |

| 2.2.           | PWM de Vector de Espacio Tradicional                                        | 20 |

| 2.2.1          | Principio de Operación                                                      | 20 |

| 2.2.2          | . Método de Implementación                                                  | 24 |

| 2.2.3          | Realización Práctica                                                        | 25 |

| 2.2.3          | .1. Generación de Voltajes en un ciclo de Conmutación                       | 25 |

| 2.2.3          | 2.2. Principio de Operación del Algoritmo de SVM para un Inversor Trifásico | 26 |

| 2.2.3          | 3.3. Generador de Portadora.                                                | 27 |

| 2.2.3          | .4. Localizador de Sector                                                   | 27 |

| 2.2.3          | 5.5. Generador de Tiempos Activos.                                          | 27 |

| 2.2.3          | 6.6. Generador de Interrupciones                                            | 28 |

| 2.3.           | Modulación de Espacio Vectorial de Ancho de pulso para otras topologías     | 28 |

| 2.3.1          | Inversores Multiniveles                                                     | 28 |

| 2.3.2          | . Inversores Asimétricos.                                                   | 28 |

| 2.3.3          | Ejemplificación de un inversor multiniveles.                                | 28 |

| 2.4.           | Resumen                                                                     | 29 |

| 2.5.           | Referencias                                                                 | 30 |

| CAPÍTU         | JLO 3                                                                       | 31 |

| 3. | Sinc    | onizador de fase cerrada                                            | 31   |

|----|---------|---------------------------------------------------------------------|------|

|    | 3.1.    | Introducción.                                                       | 31   |

|    | 3.2.    | Principio de Funcionamiento.                                        | 32   |

|    | 3.2.1.  | Marco de referencia rotante como Detector de Fase.                  | 32   |

|    | 3.2.2.  | DCO Digital.                                                        | 34   |

|    | 3.2.3.  | Compensador.                                                        | 34   |

|    | 3.3.    | Diseño del PLL.                                                     | 37   |

|    | 3.4.    | Metodología de Implementación                                       | 39   |

|    | 3.4.1.  | Descripción del PLL                                                 | 40   |

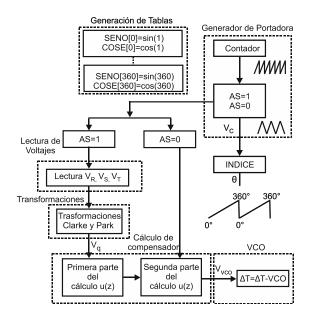

|    | 3.4.1.1 | . Generación de tablas                                              | 40   |

|    | 3.4.1.2 | . Lectura de Voltajes                                               | 40   |

|    | 3.4.1.3 | . Transformaciones                                                  | 40   |

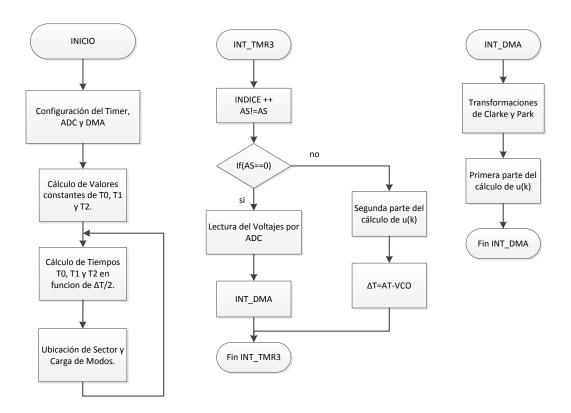

|    | 3.4.1.4 | . Cálculo de compensador                                            | 40   |

|    | 3.5.    | Resumen                                                             | . 40 |

|    | 3.6.    | Referencias.                                                        | 42   |

| C  | APÍTUL  | O 4                                                                 | 43   |

| 4. | Impl    | ementación digital                                                  | 43   |

|    | 4.1.    | Introducción                                                        | 43   |

|    | 4.2.    | Breve descripción del microcontrolador                              | . 44 |

|    | 4.3.    | Implementación de algoritmo de SVPWM                                | 45   |

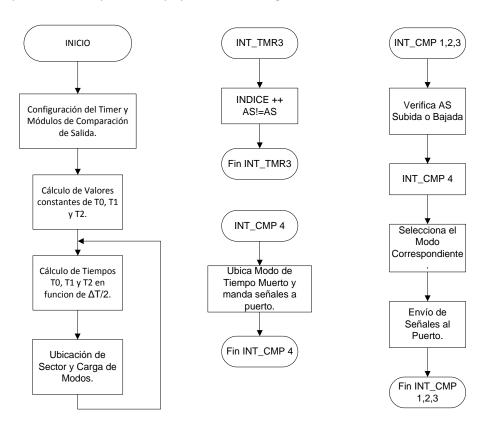

|    | 4.3.1.  | Configuración del Timer                                             | 46   |

|    | 4.3.2.  | Configuración de los Módulos de Comparación de Salida               | 47   |

|    | 4.4.    | Verificación numérica del PLL.                                      | 47   |

|    | 4.5.    | Implementación Digital del PLL                                      | 50   |

|    | 4.5.1.  | Configuración del ADC                                               | 52   |

|    | 4.5.2.  | Configuración del DMA                                               | 52   |

|    | 4.6.    | Resumen                                                             | 52   |

|    | 4.7.    | Referencias.                                                        | 53   |

| C  | APÍTUL  | O 5                                                                 | 54   |

| 5. | Prue    | bas y resultados                                                    | 54   |

|    | 5.1.    | Introducción                                                        | 54   |

|    | 5.2.    | Verificación de las señales de control para el inversor tradicional | 55   |

| 5.3.    | Verificación experimental del inversor Trifásico y la modulación SVPWM | 56 |

|---------|------------------------------------------------------------------------|----|

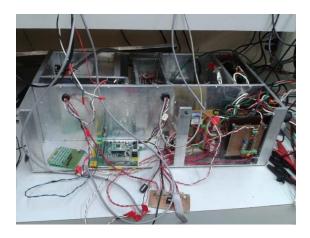

| 5.4.    | Desarrollo físico del PLL                                              | 58 |

| 5.5.    | Verificación de transformación de Clarke en el dsPIC                   | 59 |

| 5.6.    | Verificación experimental del PLL                                      | 61 |

| 5.7.    | Resumen                                                                | 66 |

| CAPÍTUI | LO 6                                                                   | 67 |

| 6. Ob:  | servaciones y Conclusiones                                             | 67 |

| 6.1.    | Introducción                                                           | 67 |

| 6.2.    | Trabajo Futuro                                                         | 68 |

| 6.3.    | Conclusiones y observaciones                                           | 68 |

| ANEXO . | A                                                                      | 69 |

| 7. Có   | digo del programa del SVPMW y PLL digital                              | 69 |

|         |                                                                        |    |

## Índice de Figuras

| Figura 1.1 a) Diagrama rectificador monofásico no controlado b) Diagrama rectificador trifásion    | co no        |

|----------------------------------------------------------------------------------------------------|--------------|

| controlado                                                                                         | 2            |

| Figura 1.2 Diagrama de un rectificador trifásico controlado                                        | 3            |

| Figura 1.3 Diagrama de un rectificador activo                                                      | 4            |

| Figura 1.4 Diagrama general de un inversor de CA-CA utilizando un inversor                         | 5            |

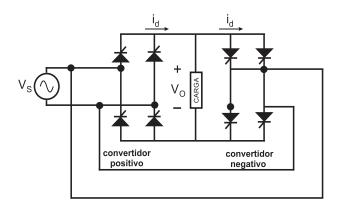

| Figura 1.5 Diagrama de un ciclo-convertidor monofásico                                             | 5            |

| Figura 1.6 Formas de onda del voltaje de salida del ciclo-convertidor con angulos de disparo o     | de           |

| α=0° y α=60°                                                                                       | <del>6</del> |

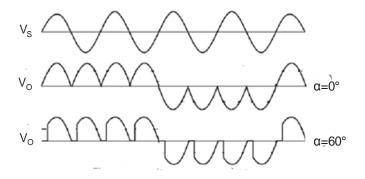

| Figura 1.7 Diagrama de un convertidor matricial                                                    | e            |

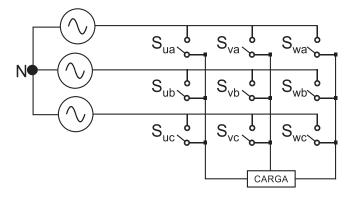

| Figura 1.8 Esquema general de un Inversor                                                          | 7            |

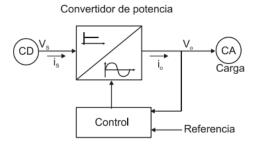

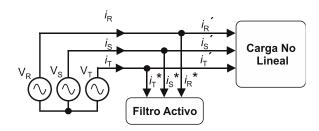

| Figura 1.9 Diagrama de un Filtro activo                                                            | 8            |

| Figura 1.10 Circuito de Interpolación de Doble Punto                                               | 9            |

| Figura 1.11 a) Circuito realimentado con histéresis. B) Comparador dinámico con histéresis         | 10           |

| Figura 1.12. a) Diagrama del PD b) Voltaje de entrada, c) Voltaje de salida d)Salida del PD        | 12           |

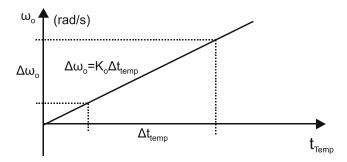

| Figura 1.13 Relación de cambio de la frecuencia $\omega_{o}$ , y el voltaje de control $V_{c}$     | 13           |

| Figura 1.14 Ganancia del VCO de acuerdo a la relación de Voltaje de salida, $vo$ , y la frecuencia | a de         |

| este voltaje $\omega o$                                                                            | 14           |

| Figura 1.15 Diagrama a bloques de un PLL                                                           | 14           |

| Figura 1.16 Cambio de coordenadas por Transformación de Clarke                                     | 15           |

| Figura 1.17 Cambio de ejes en la transformada de Park                                              | 16           |

| Figura 2.1 Inversor Trifásico Tradicional.                                                         |              |

| Figura 2.2 Combinaciones válidas para un Inversor Trifásico Tradicional                            | 20           |

| Figura 2.3 Posición de las 8 combinaciones válidas para los interruptores de un Inversor Trifás    | sico         |

| Tradicional en el plano $lpha$ - $eta$                                                             | 21           |

| Figura 2.4 Cálculo de un vector arbitrario sumando los 2 vectores estacionarios más cercanos       | 22           |

| Figura 2.5 Formas de onda de voltaje a la salida de los puentes inversores para el sector 1        | 25           |

| Figura 2.6 Diagrama a Bloques del proceso de control SVM para un Inversor Trifásico Tradicio       | nal.         |

|                                                                                                    | 26           |

| Figura 2.7 Esquema de señales de control y secuencia de interrupciones del Algoritmo para S'       |              |

|                                                                                                    | 27           |

| Figura 2.8 Inversor híbrido multiniveles                                                           | 29           |

| Figura 3.1 Diagrama a bloques del PLL Digital                                                      | 32           |

| Figura 3.2 Transformaciones de Clark y Park con una Frecuencia de entrada de 65 Hz                 | 33           |

| Figura 3.3 Transformaciones de Clark y Park con una Frecuencia de entrada de 60 Hz                 | 33           |

| Figura 3.4 Ganancia del DCO de acuerdo a la relación del tiempo del Temporizador, y la frecu       | encia        |

| que genera a la salida                                                                             | 34           |

| Figura 3.5 Respuesta en frecuencia del compensador de [3-1]                                        | 34           |

| Figura 3.6 Modelo Lineal del PLL                                                                   | 35           |

| Figura 3.7 Modelo Lineal del PLL con Laplace                                                    | 35   |

|-------------------------------------------------------------------------------------------------|------|

| Figura 3.8 Respuesta en Frecuencia de G(s).                                                     | 36   |

| Figura 3.9 Respuesta en frecuencia de <i>Hs</i>                                                 | 36   |

| Figura 3.10 Respuesta en frecuencia de lazo cerrado F(s)                                        | 37   |

| Figura 3.11 Respuesta en frecuencia de T(s)                                                     |      |

| Figura 3.12 Respuesta en frecuencia de lazo cerrado $Fs$                                        | 38   |

| Figura 3.13 Diagrama a Bloques del PLL.                                                         | 39   |

| Figura 4.1 Diagrama de Flujo que describe la forma de programación del algoritmo para un        |      |

| Inversor Trifásico Tradicional                                                                  | 45   |

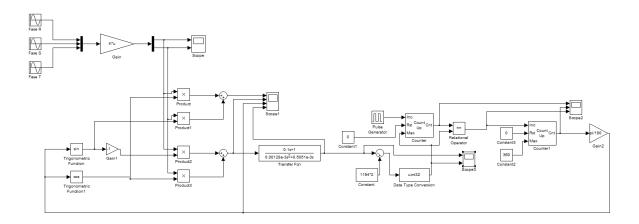

| Figura 4.2 Diagrama a bloques en SIMULINK del PLL                                               | 48   |

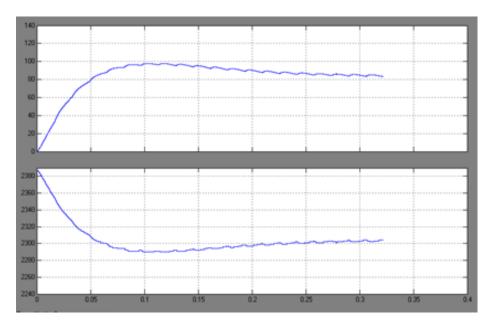

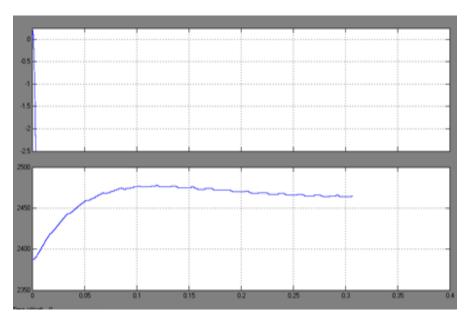

| Figura 4.3 Valor del Registro del <i>Timer</i> para una frecuencia fundamental del PLL de 62 Hz | 49   |

| Figura 4.4 Valor del Registro del <i>Timer</i> para una frecuencia fundamental del PLL de 58 Hz | 49   |

| Figura 4.5. Valor del Registro del Timer para una frecuencia fundamental del PLL de 60 Hz       | 50   |

| Figura 4.6 Diagrama a Bloques del programa                                                      | 51   |

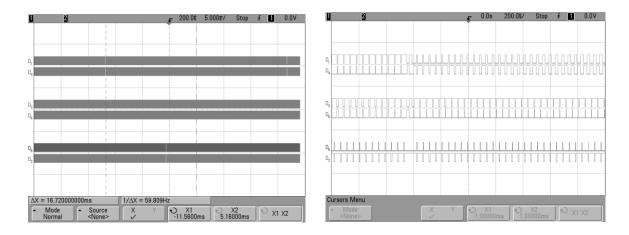

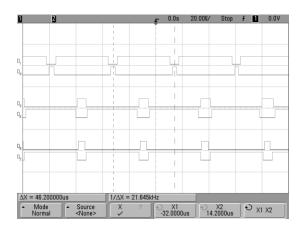

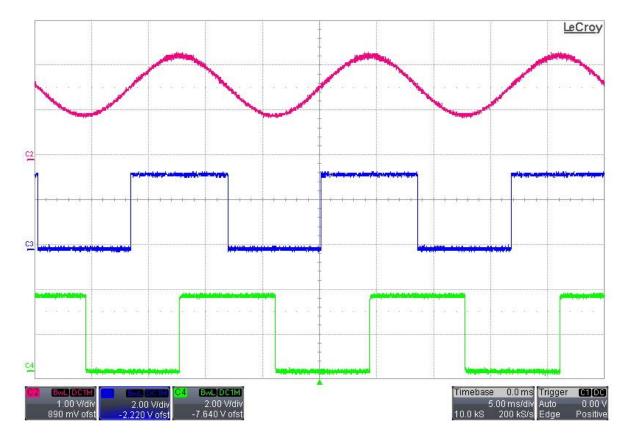

| Figura 5.5.1 a) Señales de control mostrando su frecuencia fundamental de 60 Hz b) Ampliaciór   | າ en |

| tiempo de las señales de control                                                                | 55   |

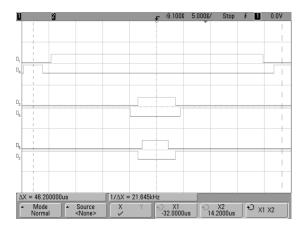

| Figura 5.2 Señales de control para el primer sextante de la SVPWM                               | 56   |

| Figura 5.3 Tiempos muertos en las señales de control                                            | 56   |

| Figura 5.4 Compuerta AND como generador de combinación de tiempo muerto                         | 56   |

| Figura 5.5 Filtro activo de potencia                                                            | 57   |

| Figura 5.6 Inversor trifásico del filtro activo.                                                | 57   |

| Figura 5.7 Diagrama a bloques del inversor                                                      |      |

| Figura 5.8 Voltajes <i>VRN, VSN</i> y <i>VTN</i> obtenidos con SVPWM                            | 58   |

| Figura 5.9 Acercamiento de los voltajes $VRN$ , $VSN$ y $VTN$ obtenidos con SVPWM               | 58   |

| Figura 5.10. Tarjeta acondicionadora de voltaje                                                 | 59   |

| Figura 5.11. dsPIC en la tarjeta de desarrollo Explorer 16 con su conector de expansión         |      |

| Figura 5.12. Comprobación de las la transformación de Clarke                                    | 60   |

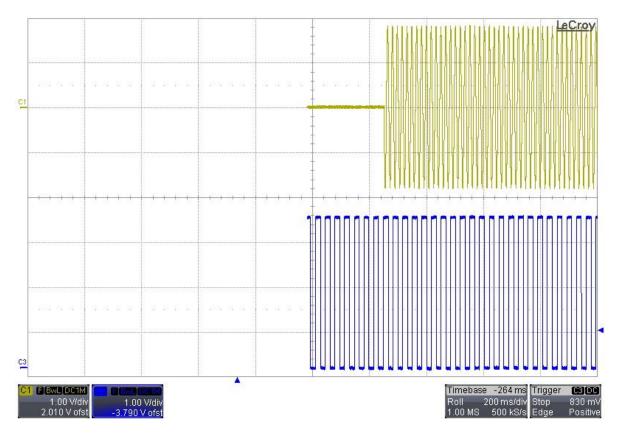

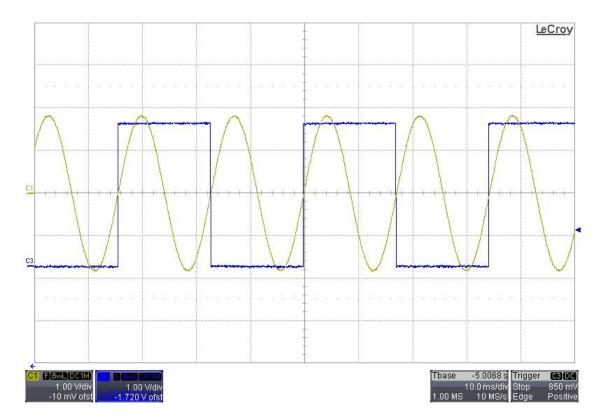

| Figura 5.13 Funcionamiento del PLL utilizando una fase y una señal cuadrada                     | 61   |

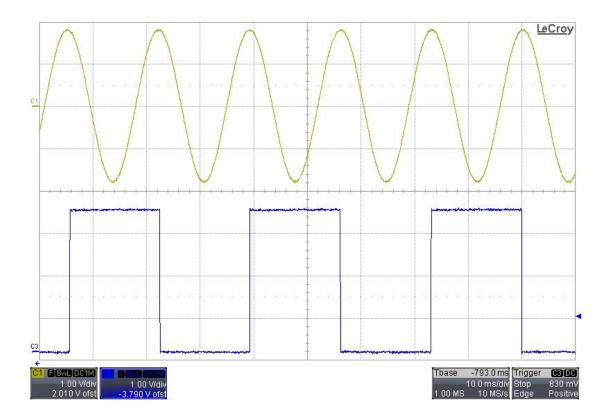

| Figura 5.14. Sincronización de la SVPWM con $\mathit{VR}$ a través del PLL digital              | 62   |

| Figura 5.15 Sincronización de la SVPWM                                                          | 63   |

| Figura 5.16 Acercamiento a las formadas de onda sincronizadas por el PLL digital                |      |

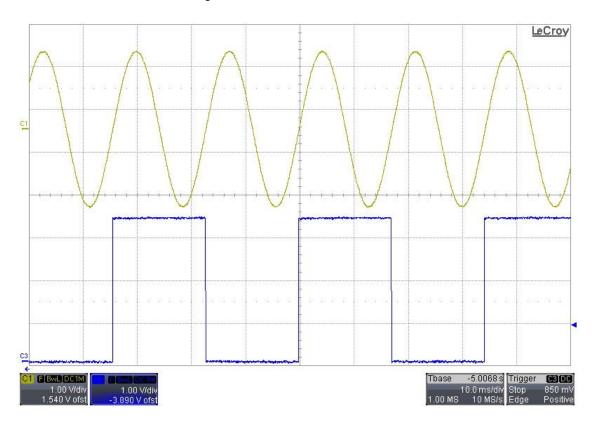

| Figura 5.17 Superposicion de la señal del PLL y $\mathit{VR}$                                   |      |

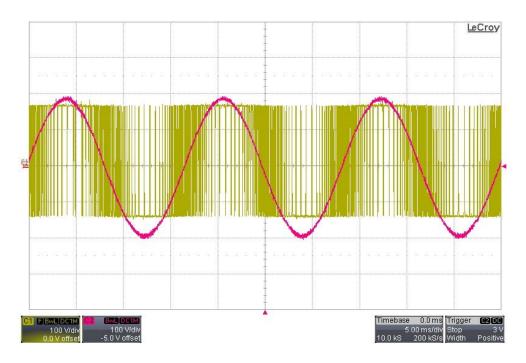

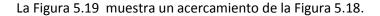

| Figura 5.18. Sincronización de $VRN \;$ con la fase R de la fuente trifásica usando el PLL      | 65   |

| Figura 5.19. Acercamiento de las señales sincronizadas.                                         | 65   |

### Índice de Tablas

| Tabla 2.1 Tabla de tiempos activos de un inversor trifásico                             | 24 |

|-----------------------------------------------------------------------------------------|----|

| Tabla 4.1 Configuración del Timer 3 para el algoritmo de SVM para el inversor Trifásico | 47 |

| Tabla 4.2 Configuración del Modulo de comparación                                       | 47 |

| Tabla 4.3 Frecuencia fundamental del PLL en relación al "Timer" del dsPIC               | 48 |

| Tabla 4.4 Configuración del ADC para el algoritmo del PLL                               | 52 |

| Tabla 4.5 Configuración del DMA para el algoritmo del PLL                               | 52 |

# **AGRADECIMIENTOS**

Al Instituto Politécnico Nacional por apoyar en la construcción del presente trabajo, mi crecimiento profesional y por brindarme todos los medios para poder conseguir esta licenciatura. Esta institución es la madre de mis conocimientos.

A la Escuela Superior de Ingeniería Mecánica y Eléctrica Unidad Culhuacan, por apoyar mi superación con sus instalaciones y permitir mi estancia durante este tiempo.

Al CONACYT y al ICyTDF por recibirme para formar parte de este proyecto y apoyar económicamente el desarrollo de esta tesis.

Al Dr. Ismael Araujo Vargas por dirigir este proyecto, por haber compartido su conocimiento y por brindarme su amistad. Es un privilegio seguir en trabajando a su lado.

Al M. en C. Alejandro Tapia Hernández por apoyarme en el desarrollo de este trabajo, porque a lo largo de este tiempo pudo resolver muchas de mis dudas compartiendo conmigo su conocimiento y amistad a pesar de sus actividades.

## DEDICATORIA

A mi Dios.

A mis padres Ariel Cano Gutiérrez y Mayra Pulido Apanco quienes siempre me brindaron todo su apoyo y amor. Gracias por el regalo de darme educación. Los amo.

A mi hermana Eli por ser mi mejor amiga. Por estar junto a mí durante toda su vida.

A mis abuelos Aarón, Libia y Clemencia, que en paz descansen y que desearon verme terminar esta etapa. A mi viejo querido Delfino Cano quien siempre me dio su cariño y me llena de consejos.

A mis amigos, Atoany, Jordan, Oso, Lalo, Chava, Jerry, Josh, Afro; quienes compartieron conmigo tantos momentos con muchos sinsabores y alegrías a lo largo de mi carrera.

A Flor que ha estado conmigo estos últimos años dándome su apoyo y cariño.

A mis amigos y compañeros en esta nueva etapa de mi vida, Niño, Onesimo, Panamá, Pancho, Jaz, Nancy, Alex, Alberto, Cid y Jose Luis.

# **RESUMEN**

En esta tesis se muestra el análisis, diseño y construcción de un PLL para un convertidor inversor controlado con Modulación de Vector de espacio. Describe la manera en la que se controla un inversor trifásico tradicional con esta modulación y se desarrolla un programa que se implementa en un microcontrolador. Además, se hace un recuento de las principales herramientas para sincronizar circuitos. De esta manera se explicar el funcionamiento de un PLL y se desarrolla uno mismo de manera digital implementado en un microcontrolador. Finalmente se muestran los resultados obtenidos de manera simulada y experimental. Este último apartado demuestra el correcto funcionamiento del PLL.

# CAPÍTULO 1

### 1. Estado del Arte

#### 1.1.Introducción.

En este capítulo se describe un breve marco teórico de los tipos de convertidores que trabajan alimentados en CA (*Corriente Alterna*). También se hace una revisión de algunas de las técnicas y circuitos de sincronización de los convertidores con fuente de suministro en CA. Además, se describen las herramientas básicas para controlar estos circuitos, como por ejemplo las transformaciones de Clarke y Park.

# 1.2. Estado del arte relativo a Convertidores electrónicos de energía que operan con suministro de CA.

Los convertidores que operan con CA pueden clasificarse según diferentes criterios. El criterio más comúnmente utilizado es agruparlos dependiendo del tipo de forma de onda de entrada o salida a operar. Básicamente, según este criterio pueden establecerse cuatro grandes grupos:

- Rectificadores o convertidores CA-CD (Corriente Directa).

- Ciclo-convertidores o convertidores CA-CA.

- Inversores o convertidores CD-CA.

- Filtros Activos.

#### 1.2.1. Rectificadores.

En este apartado se inicia con una descripción general de los rectificadores. La distribución de la energía eléctrica se hace, esencialmente, en corriente alterna, debido principalmente a la facilidad de adaptación a diferentes niveles de voltaje por medio de transformadores. Sin embargo, en muchas aplicaciones, especialmente en aparatos electrodomésticos, la carga requiere una corriente continua. La conversión CA-CD es realizada por convertidores comúnmente denominados rectificadores. Por tanto, un rectificador es un convertidor electrónico cuya función es convertir la corriente alterna a continua.

#### 1.2.1.1. Rectificadores naturalmente controlados.

En el momento de llevar a cabo la rectificación, se utilizan elementos electrónicos que permiten el paso de la corriente en un sentido, permaneciendo bloqueado cuando se le aplica una tensión con polaridad opuesta. Para ello en los rectificadores no controlados, el componente más adecuado y utilizado es el diodo.

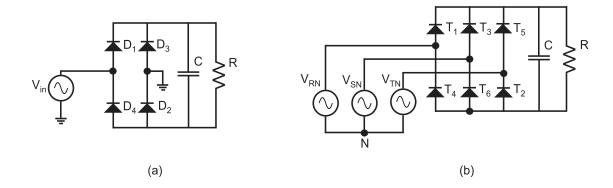

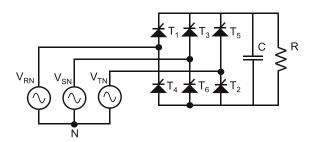

Figura 1.1 a) Diagrama rectificador monofásico no controlado b) Diagrama rectificador trifásico no controlado.

La Figura 1.1a muestra el diagrama del rectificador de onda complete. Por otro lado, la Figura 1.1b muestra un rectificador trifásico. Ambos cumplen con la misma función con la diferencia de que éstos últimos son alimentados por fuentes trifásicas, por lo que son más eficientes y pueden manejar grandes potencias, ya que en su salida presentan menor rizado de la señal. Son utilizados principalmente en la industria para producir voltajes y corrientes continuos que generalmente impulsan cargas de gran potencia, como motores CD [1-2].

#### 1.2.1.2. Rectificadores controlados.

El rectificador trifásico controlado, que se observa en la Figura 1.2, permite variar el voltaje promedio de salida, empleando para su funcionamiento tiristores de potencia con los cuales se puede variar el ángulo de disparo y la potencia entregada a la carga. Los tiristores se disparan a un intervalo de  $\frac{\pi}{3}$ .La frecuencia del rizo de voltaje en la salida es seis veces la frecuencia de la fuente de entrada (6f<sub>s</sub>), y el filtrado resulta más complejo en comparación con el de los convertidores naturalmente controlados[1-2,3].

Figura 1.2 Diagrama de un rectificador trifásico controlado.

Controlando el ángulo de disparo de los tiristores se puede controlar el valor medio de la tensión en la carga. El ángulo de disparo deseado se obtendrá generando los pulsos de disparo, que se aplican en la puerta de los tiristores, en el momento adecuado.

#### 1.2.1.3. Rectificadores activos.

La estrategia de funcionamiento de estos filtros activos se basa en la conexión en la barra de un transformador el cual es alimentado por un puente inversor a partir de un bus de CD. El inversor de compensación es controlado por un microprocesador y requiere de la medición de la corriente inyectada por el inversor y la corriente armónica a compensar. En los últimos años, los puentes rectificadores con control por ancho de pulso (PWM), han sido introducidos con la finalidad de realizar procesos de conversión AC-DC de alta calidad. Estos circuitos sólo permiten reducir el contenido de armónicos al sistema de CA de tal manera que el controlado del factor de

potencia en la barra de alimentación del puente y el voltaje de salida pueden ser controlados. En la Figura 1.3 se muestra un ejemplo de la topología básica de un rectificador activo.

Figura 1.3 Diagrama de un rectificador activo.

#### 1.2.1.4. Resumen.

De lo anterior se puede concluir que las últimas 2 categorías requieren de señales de control en sincronía y fase determinadas con la frecuencia del suministro para que estos circuitos funcionen apropiadamente.

#### 1.2.2. Ciclo-convertidores.

En contraste con los convertidores de voltaje que operan con corriente alterna a una frecuencia constante, los ciclo-convertidores realizan un transformación CA-CA cambiando la frecuencia de la tensión de salida. La aplicación típica de este circuito es en el control de velocidad de motores síncronos y de inducción por medio de variación de frecuencia. A continuación se mencionan algunos de los principales usos para estos convertidores.

- Impulsores de molinos de cemento

- Control de motores de inducción

- Propulsión de vehículos.

- Calentamiento por alta frecuencia.

- Molinos para triturar minerales.

- Excavadoras de minas.

#### 1.2.2.1. Ciclo-convertidores a base de inversores.

Tradicionalmente la conversión CA-CA se lleva a cabo en dos etapas: primero re realiza una conversión CA-CD con un rectificador y luego se realiza una conversión CD-CA mediante un inversor. La Figura 1.4

Figura 1.4 Diagrama general de un inversor de CA-CA utilizando un inversor.

#### 1.2.2.2. Ciclo-convertidores en base a tiristores.

Estos ciclo-convertidores son diseñados principalmente para evitar las dos etapas de conversión mencionadas en el apartado anterior, lo que eleva el rendimiento y reduce la cantidad de componentes necesarios. Dependiendo del número de fases del suministro se tienen diferentes topologías de este convertidor, es decir, existen convertidores monofásico y trifásicos.

La Figura 1.5 muestra un ciclo-convertidor en base a tiristores monofásico. El circuito consiste en dos rectificadores conectados al mismo suministro.

Figura 1.5 Diagrama de un ciclo-convertidor monofásico.

En el primer semiciclo se disparan los tiristores del puente llamado convertidor + quedando encendidos por una cierta cantidad de ciclos de la señal de entrada. En el segundo semiciclo funciona el convertidor – durante la misma cantidad de ciclos que el convertidor+. Así la carga recibe una tensión alterna compuesta por semiciclos de la tensión de entrada con una frecuencia que es submúltiplo de la original. Cabe destacar que para ajustar el valor RMS de la tensión de salida se varía el ángulo de disparo de los tiristores, como se observa en la Figura 1.6, con ángulos de 0° y 60°.

Figura 1.6 Formas de onda del voltaje de salida del ciclo-convertidor con angulos de disparo de  $\alpha$ =0° y  $\alpha$ =60°.

#### 1.2.2.3. Convertidores Matriciales.

Un convertidor matricial (CM) es un convertidor CA-CA trifásico que consiste en un arreglo de interruptores bidireccionales que conectan una carga trifásica e la línea de alimentación. El elemento clave en el CM es el control de los interruptores bidireccionales, mostrado en la Figura 1.7, que operan a alta frecuencia. Estos son controlados de tal manera que el CM pueda suministrar a la carga un voltaje de amplitud y frecuencia variables.

Figura 1.7 Diagrama de un convertidor matricial.

Los voltajes de salida son generados a través de patrones de modulación PWM (por sus iglas en inglés Pulse Width Modulation, Modulación de Ancho de Pulso), similares a los utilizados en inversores convencionales, excepto porque la entrada es una fuente de alimentación trifásica en lugar de un voltaje de CD. Una cualidad de estos circuitos es que se emplean arreglos complejos de transistores por cada interruptor.

#### 1.2.2.4. Resumen.

Se concluye que las señales de control que los ciclo-convertidores también requieren una sincronía con el suministro para generar las formas de onda apropiadas como por ejemplo los

convertidores matriciales. Sin embargo para el caso de convertidores de dos etapas, no es de alta importancia sincronizar el inversor con la línea a menos que la aplicación requiera que la salida tenga sincronía con el suministro.

#### 1.2.3. Inversores.

#### 1.2.3.1. Inversores.

Los convertidores de CD-CA se conocen como inversores. Se trata de un circuito encargado de generar señales de CA (preferentemente sinusoidales) que sean capaces de proporcionar suficiente potencia a la carga a partir de un suministro de CD mediante la utilización de diversas técnicas de modulación. La Figura 1.8 muestra el diagrama a bloques de un inversor [1-1].

Existen diferentes tipos de control de inversores así como de topologías, por ejemplo, resonantes, PWM, multiniveles, multipulsos, entre otros.

Figura 1.8 Esquema general de un Inversor.

En ciertas otras aplicaciones es imprescindible que la frecuencia fundamental del inversor esté sincronizada a la frecuencia de suministro, para esto se utilizan técnicas de sincronización. Algunas de las aplicaciones son los sistemas ininterrumpibles de energía, control de motores de CA, control de motores de inducción en generadores eólicos, distribución de energía eléctrica para sistemas de transporte, aeronaves entre otras. Dentro de las características que se desea tener en este tipo de convertidores es una alta eficiencia, peso ligero, tamaño reducido y bajo costo.

#### **1.2.3.2.** Resumen.

Se concluye que aunque un inversor puede determinar la frecuencia de salida, a veces es necesario sincronizarlo con la red eléctrica para aplicaciones específicas, por esta razón se desarrollan herramientas de sincronización que no solo se refieran a la frecuencia sino también a la fase.

#### 1.2.4. Filtros Activos.

Debido al alto problema que causan los armónicos en los sistemas de potencia, se han desarrollado soluciones como lo son los filtros activos.

#### 1.2.4.1. Esquema General.

Generalmente, un filtro activo se considera como una fuente de corriente conectada en paralelo con la carga. El enfoque se basa en el principio de la inyección de armónicos de corriente de magnitud y de fase inversa a la de los armónicos de la corriente de carga. La Figura 1.9 muestra el diagrama a bloques de un filtro activo paralelo [1-4].

Figura 1.9 Diagrama de un Filtro activo.

La carga no lineal hace que la corriente suministrada por el sistema trifásico se distorsione, en señales con un gran número de armónicos, el filtro inyecta armónicos de corriente, de magnitud y de fase inversa a los armónicos de la carga, haciendo que las señales de corriente sean sinusoidales.

#### 1.2.4.2. Clasificación.

Los filtros activos pueden clasificarse principalmente dependiendo de cómo se conecta el filtro respecto a la carga. Se pueden distinguir entonces filtros en serie, paralelo o mixto. Desde un punto de vista práctico, cada una de estas topologías actúa de forma distinta [1.-9]. Para la reducción de distorsión de la corriente en el punto donde se conecta el filtro se acostumbra a usar un filtro del tipo paralelo; mientras que para la reducción de la distorsión de la tensión en la carga se utilizan filtros en serie.

#### **1.2.4.3.** Resumen.

Se concluye que al tener que estar trabajando con la corriente de la línea, el filtro activo debe estar sincronizado con la misma. Esto es imprescindible ya que al tener que inyectar armónicos que cancelen a los no deseados, es necesario conocer la fase y frecuencia de la línea.

#### 1.3. Estado del arte relativo a Técnicas de sincronización de circuitos.

Existen dos técnicas generales de sincronización, éstas son el detector de cruce por cero o ZCD (por sus siglas en inglés Zero Crossing Detector) y el PLL (por sus siglas en Inglés Phase Locked Loop). La primera por ejemplo, es muy usada en aplicaciones a sistemas de voltaje monofásicos mientras que las últimas utilizan técnicas basadas en espacios vectoriales que hacen que el sistema se sincronice con voltajes trifásicos.

#### 1.3.1. Detectores de cruce por cero.

El ZCD, es el método más comun para la medicion de la frecuencia en una señal periodica. Este circuito produce un cambio de estado en su salida cuando la señal de entrada cruza por cero volts [1-6].

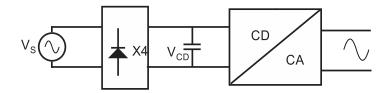

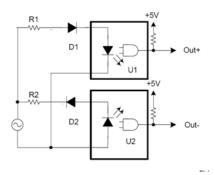

El circuito mostrado en la Figura 1.10, llamado de Interpolación de doble punto, usa dos optoacopladores para compensar variaciones en niveles de sensibilidad y tiempos de retraso en la conmutación. La implementación de este diseño identifica dos puntos en una onda sinusoidal, el primero, justo antes del cruce por cero y el segundo justo después del mismo cruce por cero.

Figura 1.10 Circuito de Interpolación de Doble Punto.

De igual manera es típico usar circuitos similares al mostrado en la Figura 1.11a para transformar los niveles de voltaje y prever inmunidad al ruido usando histéresis. Los fabricantes de estos circuitos especifican un voltaje máximo negativo en ambas entradas, positiva y negativa de 0.3 volts. Los diodos Schottky D1 y D2, mantiene el voltaje de entrada al límite del comparador de entrada por debajo de los niveles positivo y negativo. Es importante notar que este circuito es usado tanto con voltajes monofásicos y trifásicos bajo la desventaja de posibilidad de operación incorrecta en caso de distorsión, desbalance y/o desfase.

Figura 1.11 a) Circuito realimentado con histéresis. B) Comparador dinámico con histéresis.

El circuito mostrado en la Figura 1.11b es sugerido para asegurar rápidas transiciones y prevenir múltiples pulsos de salida.

#### 1.3.2. El PLL.

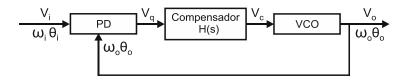

Este circuito, también llamado Sincronizador de Fase Cerrada, es un sistema retroalimentado cuyo objetivo principal consiste en la generación de una señal de salida con amplitud fija y frecuencia coincidente con la de entrada, dentro de un margen determinado. El circuito PLL comprende las siguientes tres etapas fundamentales:

- Detector de Fase (PD, por sus siglas en inglés Phase Detector). Genera una señal de salida que depende del valor absoluto del desfase entre las señales de salida y de entrada. En algunos casos, esta etapa está constituida por un multiplicador.

- Compensador (Filtro de Lazo). Ayuda a converger al sistema filtrando a la componente de baja frecuencia de la salida del PD y proporcionando la señal de control para el oscilador.

- Oscilador controlado por tensión (VCO, por sus siglas Voltage Controlled Oscillator).

Genera la frecuencia de salida, con tensión dependiente de la tensión de salida del filtro

PLL.

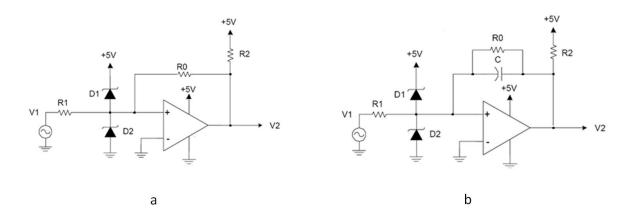

#### 1.3.2.1. Detector de Fase.

De acuerdo con [1-1], el modelo Lineal para un Detector de Fase es:

$$v_d = K_d \theta_e + V_{do} \tag{1.5}$$

donde  $K_d$  es la ganancia del PD,  $\theta_e$  es el error de fase de la salida del VCO respecto a la señal de entrada, y  $V_{do}$  es el nivel de CD del voltaje. El valor de  $\theta_e$  para el cual el Modelo Lineal es válido es llamado el rango del PD.

Un multiplicador actúa como un PD por la identidad trigonométrica

$$\sin(A)\cos(B) = 0.5\sin(A - B) + 0.5\sin(A + B) \tag{1.6}$$

Si las señales de entrada son:

$$v_i = V_i \sin(\omega_i t) \tag{1.7a}$$

$$v_o = V_o \cos(\omega_i t - \theta_e) \tag{1.7b}$$

La salida del multiplicador será:

$$v_d = K_m v_i v_o \tag{1.8}$$

donde  $K_m$  es una constante asociada con el multiplicador. Esto puede verse en el diagrama de la Figura 1.11a. Las unidades de  $K_m$  son  $volts^{-1}$  puesto que  $v_d$  está dada en volts. De acuerdo a las ecuaciones 1.6, 1.7a, 1.7b y 1.8 se obtiene que:

$$v_d = K_m V_i V_o \sin(\theta_e) + 0.5 K_m V_i V_o \sin(2\omega_i t - \theta_e)$$

(1.9)

Los dos términos de la ecuación 1.8 son evidentemente dos componentes sinusoidales. Para una  $\theta_e$  constante la salida del PD deberá ser constante de acuerdo a la ecuación 1.8, y el segundo término de esta ecuación mantiene una frecuencia  $2\omega_i t$ . En la mayoría de aplicaciones de PLLs, esta frecuencia es lo suficientemente alta por lo que el segundo término no tiene efecto, en otros casos este término es removido por un filtro. En cualquier caso, solo el primer término se considera como la salida del PD:

$$v_d = 0.5 K_m V_i V_0 \sin(\theta_e) \tag{1.10}$$

Figura 1.12. a) Diagrama del PD b) Voltaje de entrada, c) Voltaje de salida d)Salida del PD.

De esta manera la salida del PD es en realidad el promedio de la salida completa de  $v_d$  y puede ser escrita como

$$v_d = V_{dm}\sin(\theta_e) \tag{1.11}$$

Donde el máximo valor de  $v_d$  es:

$$V_{dm} = 0.5 K_m V_i V_o (1.12)$$

Esta característica sinusoidal es mostrada en la Figura 1.12d. Para valores pequeños de  $\theta_e$ ,  $\sin(\theta_e) \approx \theta_e$  y por tanto:

$$v_d = 0.5 K_m V_i V_o \theta_e \tag{1.13a}$$

Comparando las ecuaciones 1.8 y 1.13a, se observa que la ganancia del PD para pequeños valores de  $\theta_e$  es:

$$K_d = 0.5 K_m V_i V_o$$

(1.13b)

Se puede notar que la ganancia del PD depende de la amplitud de las señales de entrada.

#### 1.3.2.2. EL VCO.

El VCO es un oscilador electrónico diseñado para ser controlado a alguna frecuencia de oscilación en función del voltaje de entrada. El VCO oscila libremente a una frecuencia, determinada por una red RC o LC, llamada frecuencia central  $\omega_c$ . Esta frecuencia es comparada con la frecuencia  $\omega_i$  de la señal de entrada del detector de fase, el cual entrega una mezcla de ambas  $\omega_i - \omega_o$  o  $\omega_o - \omega_i$  dependiendo de cual es mayor. Los productos de altas frecuencias como  $\omega_i + \omega_o$ ,  $2\omega_i$ ,  $2\omega_o$ , etc. son eliminados por el compensador H(s).

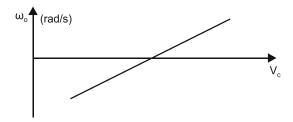

Una característica típica de un VCO es que su frecuencia  $\omega_o$  es una función lineal del voltaje de control  $v_c$  como se observa en la Figura 1.13.

Figura 1.13 Relación de cambio de la frecuencia  $\omega_{o}$ , y el voltaje de control  $V_{c}$ .

Si la frecuencia de la señal  $V_q$  es lo suficientemente baja para que el filtro pasabajas no lo atenúe ni la desfase en exceso,  $v_c$  controlará el VCO, tendiendo a reducir la diferencia de frecuencias hasta que se igualen.

Una vez que se sincronizan  $v_o$  y  $v_i$ , es decir  $\omega_i=\omega_o$ , el detector de fase entrega una tensión  $V_c$ , con una componente continua estable necesaria para que el VCO iguale la frecuencia de la señal de referencia. Esto es, como se observa en la Figura 1.13, si el voltaje,  $V_c$ , varia, entonces la frecuencia,  $\omega_o$ , también varía de acuerdo a la relación que muestra la pendiente. En este caso se establece una diferencia de fase  $\theta_e$  para producir la tensión  $V_e$  antedicha.

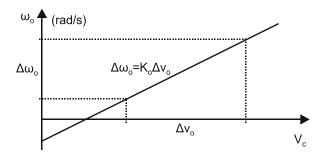

El rango de captura de un PLL depende de las características del VCO, de acuerdo al voltaje  $V_c$  y la frecuencia de operación del VCO es posible observar que existe una relación como se muestra en la ecuación 1.14.

$$\Delta\omega_o = K_o \Delta v_o \tag{1.14}$$

En donde  $\Delta\omega_o$  es el rango de captura del PLL,  $\Delta v_o$  es el rango de voltaje en que opera el VCO de acuerdo a  $\Delta\omega_o$ , mientras que  $K_o$  es la pendiente que representa la ganancia del VCO.

Figura 1.14 Ganancia del VCO de acuerdo a la relación de Voltaje de salida,  $v_o$ , y la frecuencia de este voltaje  $\omega_o$ .

#### 1.3.2.3. Compensador.

El compensador tiene dos importantes funciones. Primero, elimina el ruido y cualquier componente de alta frecuencia de la salida del detector de fase, tales como  $\omega_i + \omega_o$ , armónicas de  $\omega_i$  y  $\omega_o$ , etc., dejando pasar solo la componente de baja frecuencia  $\omega_i - \omega_o$  y  $\omega_o - \omega_i$  cuando se está adquiriendo el estado fijo, una señal continua, o pequeñas variaciones cuando el PLL ya está en estado fijo. Segundo, es el bloque más importante en la determinación de las características dinámicas del lazo, rango de captura y respuesta en frecuencia.

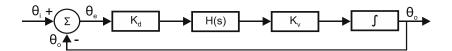

Figura 1.15 Diagrama a bloques de un PLL.

# 1.3.3. Herramientas modernas para manipular y procesar señales trifásicas en convertidores de energía.

#### 1.3.3.1. Transformación de Clarke.

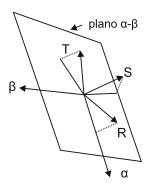

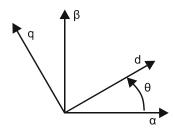

La transformación de Clarke transforma las variables eléctricas de un sistema trifásico con fases R-S-T en otras  $\alpha$ - $\beta$  que representan un sistema bidimensional de coordenadas fijo. Geométricamente supone la proyección de los ejes trifásico R-S-T sobre dos ejes  $\alpha$ - $\beta$ .

Para entender el principio de operación de esta transformación se debe considerar un sistema trifásico simétrico y balanceado, en él se puede demostrar que las corrientes y tensiones trifásicas del sistema se pueden representar mediante un vector espacial de amplitud y velocidad constantes en el plano  $\alpha$ - $\beta$  como el mostrado en la Figura 1.15. En primer lugar definimos una tensión trifásica de amplitud constante cuyas componentes sinusoidales, R, S y T, están desfasadas 120° con una amplitud máxima  $V_{max}$ , tal como se muestra en la ecuación 1.1

$$v(t) = \begin{bmatrix} v_R \\ v_S \\ v_T \end{bmatrix} = \begin{bmatrix} V_{max} \operatorname{sen}(\omega t) \\ V_{max} \operatorname{sen}(\omega t - 2\pi/3) \\ V_{max} \operatorname{sen}(\omega t + 2\pi/3) \end{bmatrix}$$

(1.1)

donde se cumple la siguiente condición:

$$V_R + V_S + V_T = 0 (1.2)$$

Por convención [1-5], se asume que la proyección del eje de la fase R en el plano  $\alpha$ - $\beta$  forma el eje de referencia  $\alpha$ . El segundo eje del plano  $\alpha$ - $\beta$  está definido de tal manera que es ortogonal al eje  $\alpha$ , y el producto cruz  $\alpha$  x  $\beta$  forma un tercer eje, que es normal al plano  $\alpha$ - $\beta$ , conocido como nulo o de secuencia cero, tal como se ve en la Figura 1.16

Figura 1.16 Cambio de coordenadas por Transformación de Clarke.

De esta manera, la transformación de Clarke está dada por la ecuación 1.2.

$$V(\alpha,\beta) = \frac{2}{3} \begin{bmatrix} 1 & -\frac{1}{2} & -\frac{1}{2} \\ 0 & \sqrt{3}/2 & -\frac{\sqrt{3}}{2} \end{bmatrix} \begin{bmatrix} V_R \\ V_S \\ V_T \end{bmatrix}$$

(1.3)

#### 1.3.3.2. Transformación de Park.

Una vez hecho el cambio de ejes, las tensiones giraran con velocidad angular constante  $\omega$  sobre el plano definido por los ejes  $\alpha$ - $\beta$ . El principal interés en la transformación de Park es establecer los vectores espaciales de voltaje en una determinada posición, de modo que se busque identificar una diferencia entre dos diferentes velocidades angulares. La transformación de Park convierte dos fases de un plano estacionario ( $\alpha$ - $\beta$ ) en dos fases de un plano rotante (d-q). La Figura 1.17 muestra cómo se realiza el cambio de ejes.

Figura 1.17 Cambio de ejes en la transformada de Park.

A partir del ángulo de rotación de los ejes d-q, se puede definir la ecuación 1.3 que permite el cambio del plano  $\alpha$ - $\beta$  al plano d-q.

$$V(d,q) = \begin{bmatrix} \cos \theta_o & \sin \theta_o \\ -\sin \theta_o & \cos \theta_o \end{bmatrix} \begin{bmatrix} V_{\alpha} \\ V_{\beta} \end{bmatrix}$$

(1.4)

#### 1.4. Resumen del estado del arte.

Existen diferentes tipos de convertidores los cuales son necesariamente sincronizados a la red eléctrica para generar voltajes síncronos a la misma. De esta manera, es necesario conocer y entender las estrategias de modulación de cada uno de estos convertidores. Además, es de suma importancia conocer las técnicas de sincronización existentes.

Las dos principales técnicas de sincronización son el Detector de cruce por cero (ZCD) y el PLL. El ZCD suele ser empleado para sincronizamiento en sistemas monofásicos, pero es muy sensible a las variaciones causadas por ruido eléctrico, por otra parte el PLL se utiliza en sistemas trifásicos empleando técnicas como las transformaciones de Clarke y de Park las cuales crean componentes virtuales para sincronizarse a los tres voltajes.

#### 1.5.Objetivo.

Analizar, diseñar y construir un PLL Digital implementándolo en un microcontrolador que sincronice un inversor con modulación de vector de espacio, a la red eléctrica trifásica

convencional. Este circuito puede ser utilizado en otro tipo de convertidores con diferentes topologías y cambiando la estrategia de modulación. Cabe destacar que la lógica de éste, será diseñada para poder ser implementada en algún otro microcontrolador con mejores características y velocidades similares.

#### 1.6. Bosquejo.

El desarrollo de esta tesis se basa primeramente en la revisión literaria, capítulo 1, de los tipos de convertidores que utilizan voltajes de CA y que por necesidad deben ser sincronizados a alguna frecuencia externa, siendo la frecuencia de la red eléctrica la más comúnmente utilizada. Además se hace hincapié en los principales métodos de sincronización existentes y se realiza una comparación de estos. Se presentan además algunas técnicas numéricas modernas utilizadas en los métodos de sincronización.

El capítulo 2 describe el principio de operación de la Modulación de vector de espacio. Se hace referencia a un inversor tradicional y se describe paso a paso la forma de obtener los tiempos activos de cada vector estacionario, además se muestra a detalle el procedimiento a seguir para implementar esta modulación en base a un algoritmo de control.

El capítulo 3 explica el funcionamiento de un PLL y hace una descripción de sus componentes, Además se muestra paso a paso el procedimiento para calcular los valores de los componentes a una frecuencia necesaria de operación que estará sincronizada y dependerá de la Modulación de vector de espacio. Se desarrolla también un algoritmo de implementación en base a un diagrama a bloques.

En el capítulo 4 se desarrolla la implementación digital de los algoritmos descritos en los capítulos 1 y 2. Se hace también una comprobación numérica de los valores obtenidos en los cálculos previos.

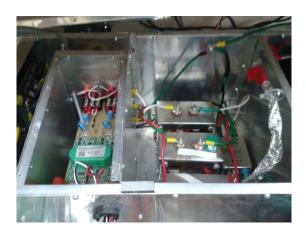

El capítulo 5 muestra las conclusiones generales de la tesis. En este apartado se pueden observar todas las formas de onda utilizadas en el desarrollo del PLL y la Modulación. Se pueden observar fotografías de los circuitos desarrollados y la formas de onda que comprueban los resultados experimentales de este trabajo.

#### 1.7. Referencias.

- N. Mohan, T.M. Undeland and W.P. Robbins, "Power Electronics", 2<sup>nd</sup> Edition, Wiley, USA, 1989.

- [1-2] M.h: Rashid, "Electrónica de Potencia", 3<sup>rd</sup> Edition, Pearson-Prentice Hall, México, 2004.

- J.G. Kassakian, M.F. Schlecht G.C. Verghese, "Principles of Power Electronics", Addison-[1-3] Wesley, 1991.

- Benslimane T., Aliouane K., "A new optimized SVPWM technique control for [1-4] autonomous parallel active filter.", Power electronics Laboratory, E. M. P.

- D. Grahame Holmes, Thomas A. Lipo, "Pulse width modulation for power converters

- [1-5] Principles and Practice", IEEE series on Power Engineering, Mohamed E. El-Hawary, series editor.

- [1-6] Wall R.W., "Simple methods for detecting zero crossing", Senior Member, IEEE.

- Pindado R., "Phase Locked-Loop (PLL): Fundamento y aplicaciones", Universidad [1-7]

Politécnica de Cataluña.

- [1-8] Wolaver, Dan H. "Phase-Loocked Loop Circuit design". Prentince Hall.

- Petit Suárez, J. Farith, "Topologías y algoritmos de control para filtros activos aplicados a [1-9] la mejora de la calidad de suministro eléctrico", Universidad Carlos III de Madrid.

# CAPÍTULO 2

# 2. Modulación de vector de espacio de ancho de pulso.

#### 2.1.Introducción.

En este capítulo se describe el principio de operación de la Modulación de Vector de Espacio de Ancho de Pulso (SVPWM, por sus siglas en Inglés Space Vector Pulse Width Modulation). Esta descripción parte del principio de operación del Inversor Trifásico Tradicional, el cual se utiliza para el control de dispositivos semiconductores. La principal característica del SVPWM es el uso de un índice de modulación para controlar la amplitud del voltaje a la salida del inversor.

#### 2.2.PWM de Vector de Espacio Tradicional.

#### 2.2.1. Principio de Operación.

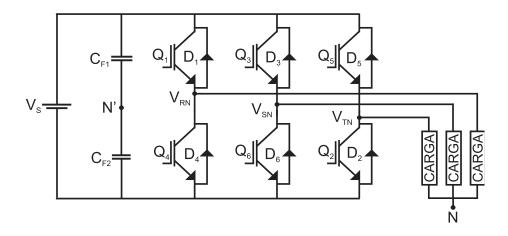

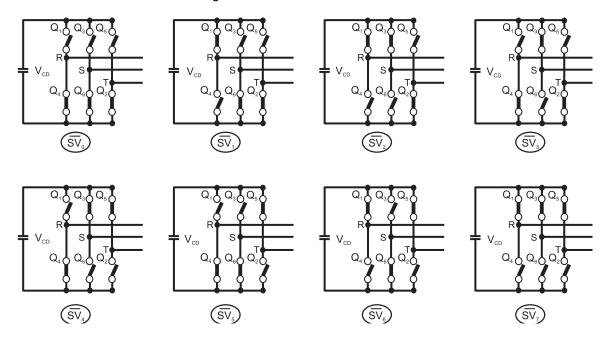

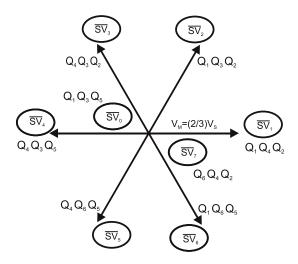

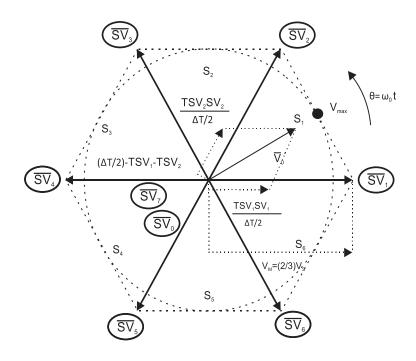

El principio de la Modulación de Vector de Espacio (SVM) se basa en un inversor tradicional como el mostrado en la Figura 2.1, en donde existen ocho posibles combinaciones, las cuáles se muestran en la Figura 2.2. Dos de estos estados ( $\overrightarrow{SV_0}$  y  $\overrightarrow{SV_7}$ ) corresponden a un voltaje nulo de salida, también conocido como Vector Neutro; las seis combinaciones restantes ( $\overrightarrow{SV_1}$  a  $\overrightarrow{SV_6}$ ) se conocen como Vectores Estacionarios [2-1].

Figura 2.1 Inversor Trifásico Tradicional.

Figura 2.2 Combinaciones válidas para un Inversor Trifásico Tradicional.

Las ocho posibles combinaciones de la Figura 2.2 pueden formar un vector de Voltaje de Salida  $\overrightarrow{V_0} = [v_{RN}, v_{SN}, v_{TN}]$ , referido al nodo N' del circuito de la Figura 2.1, el cual puede ser transformado al plano  $\alpha$ - $\theta$  mediante la siguiente ecuación de trasformación:

$$V(\alpha,\beta) = \frac{2}{3} \begin{bmatrix} 1 & -\frac{1}{2} & -\frac{1}{2} \\ 0 & \sqrt{3}/2 & -\frac{\sqrt{3}}{2} \end{bmatrix} \begin{bmatrix} V_R \\ V_S \\ V_T \end{bmatrix}$$

(2.1)

donde  $V(\alpha,\beta)$  es un espacio vectorial de dos dimensiones [2-2]. La Figura 2.3 muestra la transformación en el plano  $\alpha$ - $\theta$  en donde se presentan los 8 vectores de salida de espacio vectorial. En este mismo plano puede apreciarse que la magnitud de los Vectores Estacionarios es de  $V_M=\frac{2}{3}\,V_S$ , la cual está dada por la ecuación (2.1). Los vectores estacionarios están situados a 60° de separación a lo largo del plano  $\alpha$ - $\theta$  generando 6 sectores, con una dirección en sentido opuesto al de las manecillas del reloj.

Figura 2.3 Posición de las 8 combinaciones válidas para los interruptores de un Inversor Trifásico Tradicional en el plano  $\alpha$ - $\theta$ .

Una vez identificados los 6 vectores estacionarios, se forma el vector arbitrario  $\overline{V_o^*}$  para cualquier sector,  $S_1-S_6$ , con la capacidad de cambiar su amplitud y su ángulo. El vector arbitrario  $\overline{V_o^*}$  está compuesto de cuatro vectores locales dependiendo del sector en que se encuentre, es decir, se construye por proyecciones de los vectores estacionarios de voltaje y los vectores neutros de voltaje. Por ejemplo, en la Figura 2.4 se muestra el vector arbitrario  $\overline{V_o^*}$  para el Sector 1, el cual se construye con las proyecciones de los vectores estacionarios de voltaje más cercanos,  $\overline{SV_1}$  y

$\overrightarrow{SV_2}$ . Los vectores de proyección que forman  $\overline{V_o^*}$  cambian dependiendo la posición angular en que se encuentre  $\theta$ , donde  $\theta=\omega_o t$ ,  $\omega_o=2\pi f_o$  y  $f_o$  es la frecuencia de salida del inversor. La amplitud máxima que puede tomar el vector  $\overline{V_o^*}$  es  $V_M$ , y corresponde a la distancia que existe desde el origen del plano  $\alpha$ - $\theta$  hasta el punto medio de la unión de los vértices del hexágono causado por los vectores de espacio estacionarios. Por lo tanto  $\overline{V_o^*}$  debe tener un valor menor a  $V_M$ .

Figura 2.4 Cálculo de un vector arbitrario sumando los 2 vectores estacionarios más cercanos.

Promediando a  $\overline{V_o^*}$  para el periodo de conmutación  $\Delta T/2$  de los vectores estacionarios, la suma geométrica mostrada en la Figura 2.3 se puede expresar matemáticamente como se muestra en la ecuación (2.2).

$$\overline{V_o^*} = \frac{T_{SV_1}}{\Delta T/2} \overline{SV_1} + \frac{T_{SV_2}}{\Delta T/2} \overline{SV_2}$$

(2.2)

Cuatro diferentes periodos de tiempo componen a  $\Delta T/2$ , estos tiempos se muestran en la ecuación (2.3).

$$\frac{\Delta T}{2} = T_{SV_1} + T_{SV_2} + T_{SV_{01}} + T_{SV_{02}} \tag{2.3}$$

donde  $T_{SV_{01}}$  y  $T_{SV_{02}}$  son la duración de los tiempos de los vectores neutros  $\overline{SV_0}$  y  $\overline{SV_7}$  respectivamente.  $T_{SV_1}$  es el tiempo para el cual el vector estacionario  $\overline{SV_1}$  es seleccionado y  $T_{SV_2}$  es para el cual el vector estacionario  $\overline{SV_2}$  es seleccionado.

Tomando en cuenta que el vector arbitrario  $\overline{V_o^*}$  depende de la amplitud y posición angular dentro del plano  $\alpha$ - $\theta$ ,  $\overline{V_o^*}=V_o \rfloor \theta$  , la ecuación (2.3) se puede expresar en forma polar de la siguiente manera.

$$\frac{\Delta T}{2} V_o \left[ \theta = T_{SV_1} \overline{SV_1} + T_{SV_2} \overline{SV_2} \right] \tag{2.4}$$

donde,  $\theta = \left[0, \frac{\pi}{3}\right]$  para el Sector 1.

Sustituyendo  $\overline{SV_1} = V_M \rfloor 0$  y  $\overline{SV_2} = V_M \rfloor^{\pi}/3$  en su forma polar dentro de la ecuación (2.4), se obtiene la ecuación (2.5).

$$\frac{\Delta T}{2}V_o(\cos\theta + j\sin\theta) = T_{SV_1}\overline{SV_1}(\cos0 + j\sin0) + T_{SV_2}\overline{SV_2}\left(\cos\frac{\pi}{3} + j\sin\frac{\pi}{3}\right)$$

(2.5)

Agrupando las partes reales y las partes imaginarias de la ecuación 2.5 y utilizando las propiedades trigonométricas adecuadas, se obtienen los tiempos activos  $T_{SV_1}$  y  $T_{SV_2}$  de los vectores estacionarios  $\overline{SV_1}$  y  $\overline{SV_2}$ .

$$T_{SV_1} = \Delta T \frac{V_o}{V_M} \cos(\theta_o - \frac{\pi}{6}) \; ; \; T_{SV_2} = \Delta T \frac{V_o}{V_M} \cos(\theta_o - \frac{\pi}{2})$$

(2.6)

El mismo procedimiento se puede aplicar para obtener los tiempos activos  $T_{SV_3}-T_{SV_6}$ , usando las ecuaciones (2.2) y (2.5).

La Tabla 2.1 muestra los componentes de los vectores estacionarios más cercanos usados para calcular cualquier vector arbitrario de cualquier ángulo junto con la expresión apropiada que define el intervalo de tiempo activo para cada vector estacionario.

| Sector | $\omega\theta_0=t$                             | Vectores<br>Estacionarios                             | Tiempos activos de los vectores estacionarios                                                                                                |

|--------|------------------------------------------------|-------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|

| 1      | $0 \le \theta_0 < \frac{\pi}{3}$               | $\overrightarrow{SV_1}$ $\overrightarrow{SV_2}$       | $T_{SV_1} = \Delta T \frac{V_o}{V_M} \cos(\theta_o - \frac{\pi}{6})$ $T_{SV_2} = \Delta T \frac{V_o}{V_M} \cos(\theta_o - \frac{\pi}{2})$    |

| 2      | $\frac{\pi}{3} \le \theta_0 < \frac{2\pi}{3}$  | $\frac{\overrightarrow{SV_2}}{\overrightarrow{SV_3}}$ | $T_{SV_2} = \Delta T \frac{V_o}{V_M} \cos(\theta_o - \frac{\pi}{6})$ $T_{SV_3} = \Delta T \frac{V_o}{V_M} \cos(\theta_o - \frac{5\pi}{6})$   |

| 3      | $\frac{2\pi}{3} \le \theta_0 < \pi$            | $\overrightarrow{SV_3}$ $\overrightarrow{SV_4}$       | $T_{SV_3} = \Delta T \frac{V_o}{V_M} \cos(\theta_o - \frac{\pi}{2})$ $T_{SV_4} = \Delta T \frac{V_o}{V_M} \cos(\theta_o - \frac{7\pi}{6})$   |

| 4      | $\pi \le \theta_0 < \frac{4\pi}{3}$            | $\overline{SV_4}$ $\overline{SV_5}$                   | $T_{SV_4} = \Delta T \frac{V_o}{V_M} \cos(\theta_o - \frac{5\pi}{6})$ $T_{SV_5} = \Delta T \frac{V_o}{V_M} \cos(\theta_o - \frac{3\pi}{2})$  |

| 5      | $\frac{4\pi}{3} \le \theta_0 < \frac{5\pi}{3}$ | $\overrightarrow{SV_5}$ $\overrightarrow{SV_6}$       | $T_{SV_5} = \Delta T \frac{V_o}{V_M} \cos(\theta_o - \frac{7\pi}{6})$ $T_{SV_6} = \Delta T \frac{V_o}{V_M} \cos(\theta_o - \frac{11\pi}{6})$ |

| 6      | $\frac{5\pi}{3} \le \theta_0 < 2\pi$           | $\overline{SV_6}$ $\overline{SV_1}$                   | $T_{SV_6} = \Delta T \frac{V_o}{V_M} \cos(\theta_o - \frac{3\pi}{2})$ $T_{SV_1} = \Delta T \frac{V_o}{V_M} \cos(\theta_o - \frac{\pi}{6})$   |

Tabla 2.1 Tabla de tiempos activos de un inversor trifásico.

#### 2.2.2. Método de Implementación.

Una técnica de implementación de la SVM es centrando el vector de espacio activo en la mitad del periodo de conmutación y divide el tiempo restante del espacio del vector neutro en partes iguales entre  $\overrightarrow{SV_0}$  y  $\overrightarrow{SV_7}$ . Esto crea una secuencia de vectores de espacio para  $0 \le \theta_o \le \pi/3$  en el siguiente orden:

$$\overrightarrow{SV_0} \rightarrow \overrightarrow{SV_1} \rightarrow \overrightarrow{SV_2} \rightarrow \overrightarrow{SV_7} \rightarrow \overrightarrow{SV_7} \rightarrow \overrightarrow{SV_7} \rightarrow \overrightarrow{SV_2} \rightarrow \overrightarrow{SV_1} \rightarrow \overrightarrow{SV_0}$$

$$\Delta T/2 \rightarrow \Delta T/2$$

la cual es similar a la secuencia producida por una PWM regularmente muestreada a excepción del espacio correspondiente al vector neutro.

Una secuencia similar se establece para el resto de los sectores, usando los dos vectores de espacio más cercanos para cada sextante. La Figura 2.5 muestra el patrón de los pulsos en el primer sextante para una SVM convencional con los vectores neutros  $\overrightarrow{SV_0}$  y  $\overrightarrow{SV_7}$  espaciados igualmente.

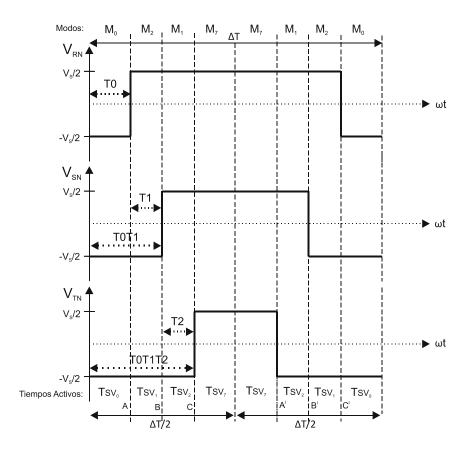

Figura 2.5 Formas de onda de voltaje a la salida de los puentes inversores para el sector 1.

Esta figura también presenta en la parte inferior los tiempos activos  $T_{SV_0}$ ,  $T_{SV_2}$ ,  $T_{SV_1}$  y  $T_{SV_7}$ , para la generación de los voltajes neutros, mientras que en la parte superior se observan los modos correspondientes para el primer sector.

#### 2.2.3. Realización Práctica.

#### 2.2.3.1. Generación de Voltajes en un ciclo de Conmutación.

Para generar las formas de onda de voltaje  $v_{RN}$ ,  $v_{SN}$  y  $v_{TN}$  en un periodo  $\Delta T$ , para el i-ésimo ciclo de conmutación centrado en un ángulo  $\theta_i$  como el que se muestra en la Figura 2.5, es necesario tomar en cuenta los modos  $M_{n+1}$  y  $M_n$  del sector en el que se encuentra el vector arbitrario, ya que de esta manera se producirán los vectores de espacio  $SV_n$  y  $SV_{n+1}$ . Las formas de

onda de voltaje de la Figura 2.5 son generadas de acuerdo a los vectores de estado de los transistores. Al inicio del periodo se observa que está activado el modo  $M_0$ , provocando que las salidas de voltaje del inversor sean de  $-{\rm V_s/2}$  durante el tiempo activo  $T_{SV_0}$ , al llegar a la transición de los modos  $M_0$  y  $M_2$ , los vectores de estado cambian de posición de acuerdo a  $M_2$  provocando que el voltaje  $V_{RN}$  conmute de  $-{\rm V_s/2}$  a  ${\rm V_s/2}$  , siendo  $T_{SV_2}$  la duración de  $M_2$ . Cuando  $T_{SV_2}$  llega a su fin, se genera otro cambio de modo de  $M_2$  a  $M_1$ , provocando que el voltaje  $V_{SN}$  cambie de  $-{\rm V_s/2}$  a  ${\rm V_s/2}$  , quedando activo  $M_1$  durante el tiempo de  $T_{SV_1}$ . Al llegar  $M_1$ a su fin, el modo  $M_7$  es activado durante el tiempo  $T_{SV_7}$  creando una transición de voltaje en la salida  $V_{TN}$  de  $-{\rm V_s/2}$  a  ${\rm V_s/2}$  . Al terminar el tiempo activo  $T_{SV_7}$ , también finaliza  $\Delta T/2$  y por lo tanto el proceso de conmutación se repite pero en un orden inverso hasta completar  $\Delta T$ . Siguiendo este mismo análisis, se generan las formas de onda de voltaje para cada uno de los 6 sectores del plano  $\alpha$ - $\theta$ .

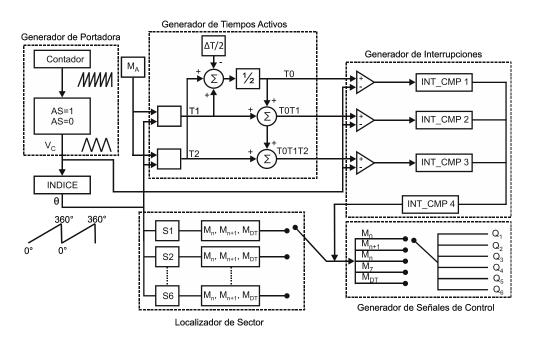

### 2.2.3.2. Principio de Operación del Algoritmo de SVM para un Inversor Trifásico.

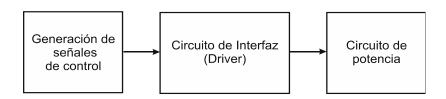

La Figura 2.6 muestra en un diagrama a bloques el proceso del algoritmo de control SVM para el Inversor Trifásico Tradicional. Este diagrama consta de 4 etapas: Generador de Portadora, Localizador de Sector, Generador de Tiempos Activos y Generador de interrupciones. A continuación se describe con detalle cada una de estas etapas.

Figura 2.6 Diagrama a Bloques del proceso de control SVM para un Inversor Trifásico Tradicional.

#### 2.2.3.3. Generador de Portadora.

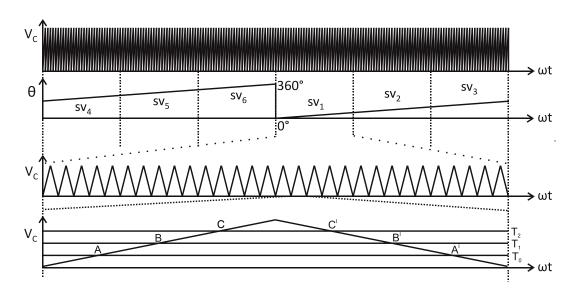

El generador de portadora crea una señal que define el orden de los pulsos de conmutación para cada sector de la SVM. La forma simétrica de esta señal triangular es creada a partir de la adjunción de dos periodos de una señal tipo "diente de sierra", la cual es generada con un contador, y definen la subida y bajada de una nueva señal triangular. Estas 2 señales son mostradas en la Figura 2.7. La frecuencia de la señal triangular está definida por el número total de pulsos por sector  $P_i$  y la frecuencia de salida  $f_{sw}=6\ f_oP$ .

Figura 2.7 Esquema de señales de control y secuencia de interrupciones del Algoritmo para SVM.

#### 2.2.3.4. Localizador de Sector.

Al cumplirse un periodo en la portadora se dispara un contador, el cual indica el sector de operación, y es representador por  $\theta$ . Este contador es equivalente a una señal escalonada con un rango de generación de 0° a 360°, el cual está dividido en 6 sectores de 60° cada uno. Dependiendo de la posición angular del Vector arbitrario  $\overrightarrow{V_o}$ , se determina el sector de operación y los modos de estado de los transistores  $M_0$ ,  $M_7$ ,  $M_{n+1}$  y  $M_n$ .

#### 2.2.3.5. Generador de Tiempos Activos.

El generador de tiempos Activos calcula los tiempos de duración T0, T1 y T2 de los modos  $M_0$ ,  $M_7$ ,  $M_{n+1}$  y  $M_n$ , ocurridos en cada sector. Los valores de T0, T1 y T2 cambian de acuerdo al Sector y al pulso  $p_i$  en el que se encuentre el vector arbitrario  $\overrightarrow{V_0}$ .

#### 2.2.3.6. Generador de Interrupciones.

Este bloque programa la ocurrencia de los eventos A, B, C, A', B', C' en el inicio del ciclo de la portadora. Esta se logra utilizando módulos de comparación-interrupción como se muestra en la Figura 2.7. Cuando  $V_C$  es igual al ángulo de los elementos A, B, C se ejecuta el cambio de modo en los transistores tomando en cuenta el ciclo de subida o bajada de la señal triangular. La Figura 2.5 muestra el resultado de los comparadores, VMOD1, VMOD2 y VMOD3, que registran los eventos A, B, C y A', B' y C', como filos de subida y filos de bajada respectivamente. Los filos de estas señales indican el cambio de modo de los transistores.

## 2.3.Modulación de Espacio Vectorial de Ancho de pulso para otras topologías.

Con el propósito de mejorar el desempeño de los inversores se han mejorado las topologías de inversores existentes. Los inversores multiniveles por ejemplo, se han aplicado especialmente para el control de motores de CA, distribución de potencia en redes de CA y fuentes de energía ininterrumpible por mencionar algunas [2-3] .

#### 2.3.1. Inversores Multiniveles.

Los inversores multiniveles están básicamente compuestos de un arreglo de capacitores en cascada como fuentes de voltaje y semiconductores de potencia. El voltaje de salida en el inversor tiene una forma escalonada dependiente de la cantidad de interruptores, lo que determina el número de niveles en la forma de onda de salida.

#### 2.3.2. Inversores Asimétricos.

El inversor asimétrico tiene como característica que los valores de sus voltajes de CD son distintos entre si. En función de la razón de sus voltajes CD existen inversores asimétricos binarios, trinarios, etc. Estos últimos tienen la cualidad de proveer una forma de onda con 3<sup>n</sup> niveles, donde n es el número de celdas conectadas en serie. Para el caso de n=3, se obtiene un voltaje de salida de 27 niveles, asegurando un voltaje con bajo contenido armónico [2-3].

#### 2.3.3. Ejemplificación de un inversor multiniveles.

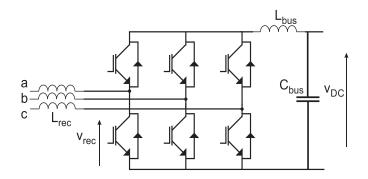

Un ejemplo de un inversor multiniveles modulado con Vector de Espacio es el inversor híbrido multiniveles mostrado en la Figura 2.8. La topología de este inversor está basada en un rectificador, el cuál fue desarrollado para aplicaciones aeroespaciales. Una descripción del

principio de operación de esta topología se encuentra en la Sección 2.2, Capítulo 2 de la referencia [2-2].

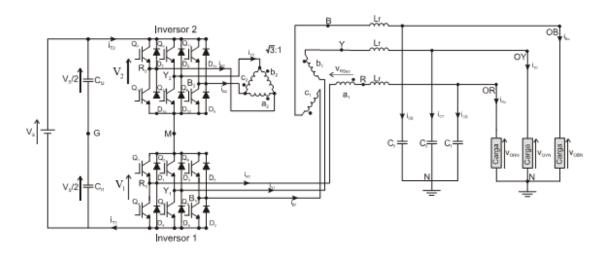

El inversor híbrido multiniveles está formado principalmente por un suministro de voltaje de corriente directa, un filtro de entrada, un arreglo de dos puentes inversores trifásicos conectados en serie, un transformador en conexión delta estrella con razón de transformación  $\sqrt{3}$ : 1 y un filtro LC para reducir el contenido armónico de las formas de onda de salida.

Figura 2.8 Inversor híbrido multiniveles.

La modulación de vector de espacio para esta topología se basa en el hecho que existen 12 configuraciones básicas del inversor y están definidas de acuerdo a los estados de los transistores de los inversores superior e inferior. La descripción de estos estados y su cálculo se describen en la referencia [2-4].

#### 2.4.Resumen.

En un inversor tradicional controlado con SVM existen ocho posibles combinaciones de voltaje a la salida. Dos de estas combinaciones son voltajes nulos a la salida, conocidos como vectores neutros, y los otros seis son vectores estacionarios. Estos vectores pueden ser controlados de manera vectorial usando algoritmos PWM. Variando el tiempo de activación de cada uno de los vectores, se puede obtener un voltaje sinusoidal a la salida. La implementación de esta modulación se puede realizar en un microcontrolador o un DSP.

#### 2.5.Referencias.

- [2-1] D. Grahame Holmes, Thomas A. Lipo, "Pulse width modulation for power converters Principles and Practice", IEEE series on Power Engineering, Mohamed E. El-Hawary, series editor.

- [2-2] Nicolas-Villalva Caren Ivet, "Modulación de Espacio Vectorial (SVM) como estrategia de control PWM para un Inversor Híbrido multiniveles", Sección de Estudios de Posgrado e Investigación, unidad Culhuacan.

- [2-3] Mondragon-Escamilla Nancy, "Análisis, diseño y construcción de un inversor multiniveles de 1kW para futuros medios de transporte", Sección de Estudios de Posgrado e Investigación, unidad Culhuacan.

- [2-4] Ramírez-Hernández Jazmín, "Modulación de espacio vectorial PWM para el control de un Inversor Híbrido multiniveles", Sección de Estudios de Posgrado e Investigación, unidad Culhuacan.

- [2-5] E. Hendawi, F. Khater, A. Shaltout, "Analysis, Simulation and Implementation of Space Vector Pulse Width Modulation Inverter", Electronics Research Institute, Cairo University.

- [2-6] K. Vinoth Kumar, Prawin Angel Michael, Joseph P. John, "Simulation ad comparison of SPWM and SVPWM control for three phase inverter". School of electrical Sciences, Karunya University, Tamilnadu, India.

- [2-7] Panda, Sunil. Mishra, Anupam. Srinivas, B. "Control of voltage inverters using PWM/SVPWM for adjustable speed drive applications". Department of Electrical Engineering National Institute of Rourkela. Rourkela.

- [2-8] Londoño N, C.Andrés. "Análisis y simulaciones de algunas estrategias de control SPWM y SVPWM en corriente para un Puente inversor" Universidad tecnológica de Pereira, Pereira.

# CAPÍTULO 3

### 3. Sincronizador de fase cerrada.

#### 3.1.Introducción.

En este capítulo se describe el principio de operación del circuito Sincronizador Digital de Fase Cerrada o PLL Digital (DPLL, por sus siglas en inglés Digital Phase Locked Loop). Este circuito se basa en el principio de funcionamiento de un PLL tradicional, cuya tecnología es ampliamente utilizada en aplicaciones militares, aeroespaciales y algunos sistemas electrónicos que buscan sincronizar su funcionamiento con un evento externo. Los orígenes de esta tecnología se remontan a la revolución industrial siendo usada por los astrónomos para observar algunas características físicas de las estrellas. En convertidores de potencia son ampliamente utilizados para la sincronización con la red eléctrica [3-1].

#### 3.2. Principio de Funcionamiento.

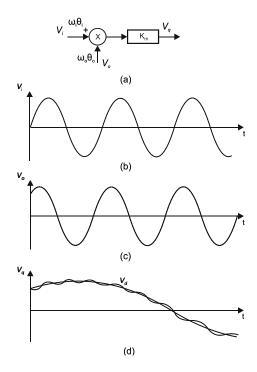

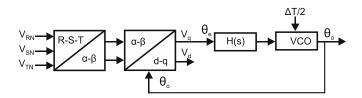

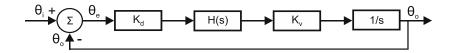

La estructura del PLL Digital está basada en el uso de un marco de referencia síncrono, un compensador y un VCO Digital como se observa en la Figura 3.1. Esta estructura está basada en la sincronización entre el vector rotante del marco de referencia y la señal de salida generada por un microcontrolador, por tanto, usando las transformaciones de Clarke y de Park, los tres valores instantáneos de voltaje son transformados a un marco de referencia rotante. Posteriormente, el compensador procesa la señal, filtrando el error y cualquier componente de alta frecuencia. Finalmente, el VCO Digital es modificado para cambiar la frecuencia fundamental de salida generada por el microcontrolador.

Figura 3.1 Diagrama a bloques del PLL Digital.

#### 3.2.1. Marco de referencia rotante como Detector de Fase.

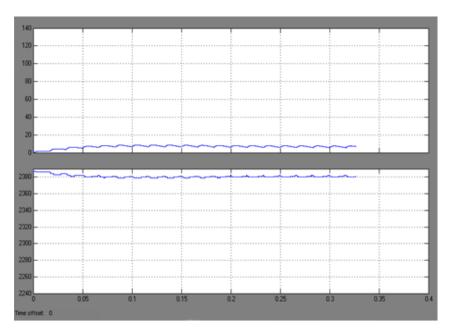

Empleado la fase de entrada de la señal generada por la transformación de Clarke,  $\theta_i$ , y el ángulo de salida del DPLL , $\theta_o$ , y aplicando la trasformación de Park se obtiene la diferencia de fase entre estos dos sistemas. Para poder entender este funcionamiento, se proponen tres señales que simulan el sistema Trifásico y dos señales, seno y coseno, que simulan el ángulo de una señal de referencia a 60 Hz, en este caso simulando el DCO, todas con una amplitud de 1 v y realizando la simulación en SIMULINK, se obtienen los resultados de las Figuras 3.2 y 3.3.

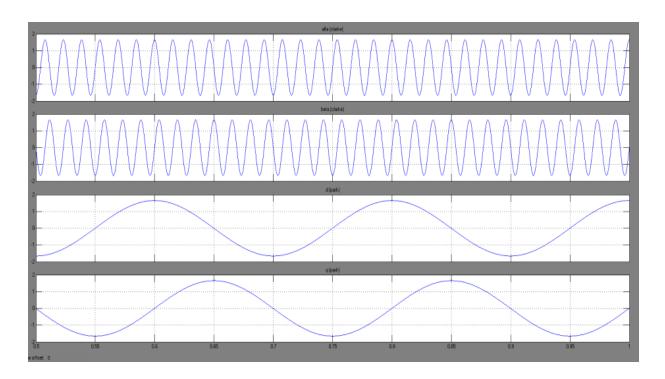

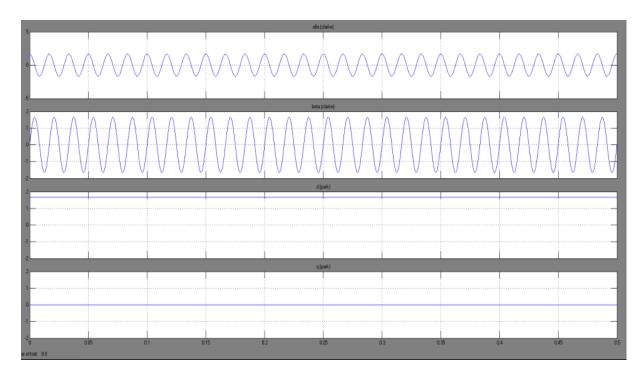

En las Figuras 3.2 y 3.3 se observa que la primer forma de onda corresponde a  $\alpha$  (Clarke), la segunda corresponde a  $\beta$  (Clarke), la tercera a d(Park) y la última a q(park). De la Figura 3.2 puede verse que si el sistema tiene frecuencias diferentes, entonces las señales d y q son oscilantes, mientas que en la Figura 3.3 cuyas frecuencias de entrada como de referencia son iguales, las señales d y q son constantes, d es uno y q es cero.

Figura 3.2 Transformaciones de Clark y Park con una Frecuencia de entrada de 65 Hz.

Figura 3.3 Transformaciones de Clark y Park con una Frecuencia de entrada de 60 Hz.

#### **3.2.2. DCO Digital.**

El DCO es un oscilador electrónico digital diseñado para trabajar con una frecuencia de oscilación en función de un temporizador, es decir, el periodo de la señal oscilante está dado por la duración del temporizador. Este tiempo está en función de la velocidad de respuesta del dispositivo electrónico utilizado ya que de esta depende el rango de frecuencias a las que el DCO es capaz de responder [3-2].

De la Figura 3.4 se observa la relación del temporizador y la frecuencia de salida del DCO.

Figura 3.4 Ganancia del DCO de acuerdo a la relación del tiempo del Temporizador, y la frecuencia que genera a la salida.

#### 3.2.3. Compensador.

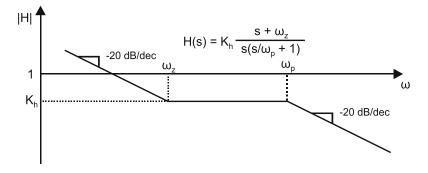

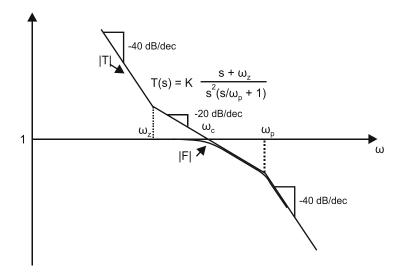

De acuerdo a [3-3], la respuesta del compensador ideal tiene una ganancia  $K_h$  desde  $\omega_Z$  hasta  $\infty$ . En la práctica, la respuesta del compensador decae hasta cierta frecuencia  $\omega_p$ , como se muestra en la Figura 3.5. La expresión de la función de transferencia de este compensador es:

$$H(s) = K_h \frac{s + \omega_z}{s(\frac{s}{\omega_p} + 1)}$$

(3.1)

Figura 3.5 Respuesta en frecuencia del compensador de [3-1].

El modelo lineal del PLL se presenta en la Figura 3.6.

Figura 3.6 Modelo Lineal del PLL.

Aplicando la transformada de Laplace se obtiene el modelo de la Figura 3.7.

Figura 3.7 Modelo Lineal del PLL con Laplace.

Si se hace que:

$$\frac{K_d K_o H(s)}{s} = T(s) \tag{3.2}$$

Sabiendo que  $\theta_e=\theta_i-\ \theta_o$ , entonces:

$$\theta_0 = T(s)\theta_e = T(s)(\theta_i - \theta_0) \tag{3.3a}$$

$$\frac{\theta_o}{\theta_i} = \frac{T(s)}{1 + T(s)} \tag{3.3b}$$

Sabiendo que  $T(s) = \frac{K_d K_o H(s)}{s}$  podemos decir que:

$$T(s) = G(s)H(s) \tag{3.4}$$

Así, se obtiene que:

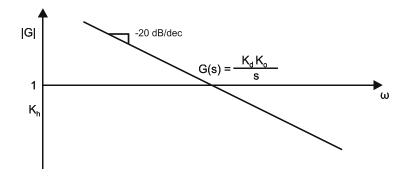

$$G(s) = \frac{K_d K_o}{s} \tag{3.5}$$

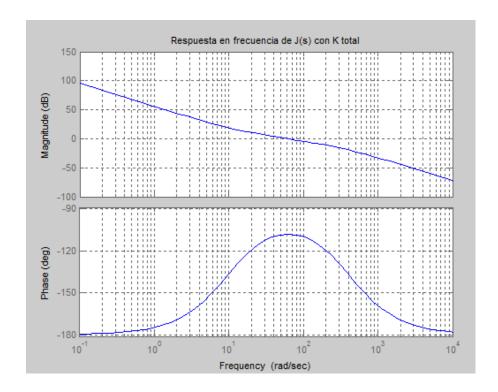

Y cuya respuesta en frecuencia pude verse en la Figura 3.8.

Figura 3.8 Respuesta en Frecuencia de G(s).

Tomando como referencia [3-3], H(s) se observa en la ecuación 3.4 y su repuesta en frecuencia se muestra en la Figura 3.9.

$$H(s) = K_{h} \frac{s + \omega_{z}}{s(\frac{s}{\omega_{p}} + 1)}$$

$$H(s) = K_{h} \frac{s + \omega_{z}}{s(s/\omega_{p} + 1)}$$

$$U_{h} = K_{h} \frac{s + \omega_{z}}{s(s/\omega_{p} + 1)}$$

Figura 3.9 Respuesta en frecuencia de H(s).

De las ecuaciones 3.4 y 3.6 se obtiene:

$$T(s) = K \frac{s + \omega_z}{s^2 (\frac{s}{\omega_p} + 1)}$$

(3.7)

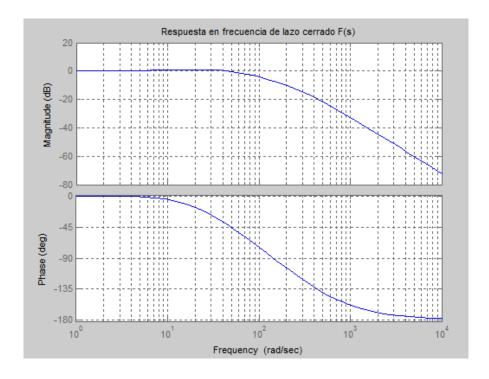

Y así, la función de transferencia del PLL viene descrita por F(s) y su respuesta en frecuencia puede verse en la Figura 3.10.

$$F(s) = \frac{\theta_o}{\theta_i} = \frac{T(s)}{1 + T(s)} \tag{3.8}$$

Figura 3.10 Respuesta en frecuencia de lazo cerrado F(s)

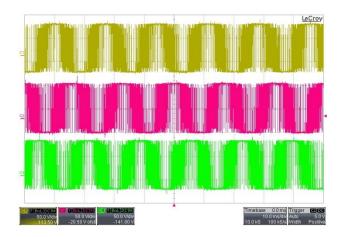

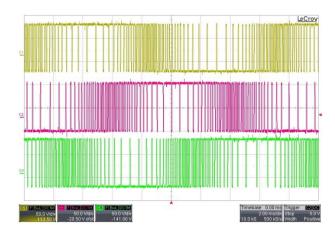

#### 3.3.Diseño del PLL.