#### INSTITUTO POLITÉCNICO NACIONAL CENTRO DE INVESTIGACIÓN Y DESARROLLO DE TECNOLOGÍA DIGITAL

#### DOCTORADO EN CIENCIAS EN SISTEMAS DIGITALES

## "DISEÑO DE CONTROLADORES PARA CONVERTIDORES DE POTENCIA"

#### **TESIS**

## QUE PARA OBTENER EL GRADO DE DOCTORADO EN CIENCIAS EN SISTEMAS DIGITALES

PRESENTA:

M. EN C. OCTAVIO AUGUSTO GARCÍA ALARCÓN

BAJO LA DIRECCIÓN DE DR. EDUARDO JAVIER MORENO VALENZUELA

#### INSTITUTO POLITÉCNICO NACIONAL

SIP-14

#### SECRETARÍA DE INVESTIGACIÓN Y POSGRADO

ACTA DE REVISIÓN DE TESIS

| En la Ciudad de                                                                                                                                                                                                                                                                                                                                                                                           | Tijuana, B.C.                         | _ siendo las     | 14:00        | horas del dí  | a 2   | 25 del     | mes d  | de   |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|------------------|--------------|---------------|-------|------------|--------|------|

| noviembre del                                                                                                                                                                                                                                                                                                                                                                                             | 2019 se reunieror                     | los miembro      | s de la Com  | nisión Revisc | ra de | e Tesis, c | lesigr | nada |

| por el Colegio de                                                                                                                                                                                                                                                                                                                                                                                         | Profesores de Estu                    | dios de Posgi    | ado e Inves  | stigación de  |       | CITE       | DI     |      |

| para examinar la<br>Diseño de control                                                                                                                                                                                                                                                                                                                                                                     | tesis titulada:<br>adores para conver | tidores de pot   | encia.       |               |       |            |        |      |

| Presentada por el a                                                                                                                                                                                                                                                                                                                                                                                       | alumno:                               |                  |              |               |       |            |        |      |

| GARCIA                                                                                                                                                                                                                                                                                                                                                                                                    |                                       | ALARCON          |              | OCTAV         | IO AI | UGUSTO     |        |      |

| Apellido paterr                                                                                                                                                                                                                                                                                                                                                                                           | no                                    | Apellido materno |              | Nombi         |       |            |        |      |

|                                                                                                                                                                                                                                                                                                                                                                                                           |                                       |                  | Con registro | o: A 1        | 6     | 0 6        | 6      | 1    |

| aspirante de:                                                                                                                                                                                                                                                                                                                                                                                             |                                       |                  |              |               |       |            |        |      |

| DOCTORADO EN                                                                                                                                                                                                                                                                                                                                                                                              | N CIENCIAS EN SI                      | STEMAS DIG       | ITALES       |               |       |            |        |      |

| DOCTORADO EN CIENCIAS EN SISTEMAS DIGITALES  Después de intercambiar opiniones, los miembros de la Comisión manifestaron APROBAR LA TESIS, en virtud de que satisface los requisitos señalados por las disposiciones reglamentarias vigentes.  LA COMISIÓN REVISORA  Director de Tesis  DR. JUAN JOSE TAPIA ARMENTA  DR. LUIS APRA AGUILAR BUSTOS  DR. MOISES SANCHEZ ADAME  DR. VICTOR HOSO DÍAZ RAMÍREZ |                                       |                  |              |               |       |            |        |      |

PRESIDENTE DEL COLEGIO DE PROFESORES

DR. JULIO CÉSAR ROLIÓN IGARRIDO CNICO NACIONAL

CENTRO DE INVESTIGACIÓN Y DESARROLLO

DE TECNOLOGÍA DIGITAL

DIRECCIÓN

#### INSTITUTO POLITÉCNICO NACIONAL SECRETARÍA DE INVESTIGACIÓN Y POSGRADO

#### CARTA CESIÓN DE DERECHOS

En la Ciudad de Tijuana, Baja California. el día 3 del mes de diciembre del año 2019, el que suscribe Octavio Augusto García Alarcón, alumno del Programa de DOCTORADO EN CIENCIAS EN SISTEMAS DIGITALES, con número de registro 160661, adscrito(a) al CENTRO DE INVESTIGACIÓN Y DESARROLLO DE TECNOLOGÍA DIGITAL, manifiesta que es el autor intelectual del presente trabajo de Tesis bajo la dirección de **Dr. Eduardo Javier Moreno Valenzuela** y cede los derechos del trabajo titulado **Diseño de controladores para convertidores de potencia**, al Instituto Politécnico Nacional para su difusión, con fines académicos y de investigación.

Los usuarios de la información no deben reproducir el contenido textual, gráficas o datos del trabajo sin el permiso expreso del (de la) autor(a) y/o director(es) del trabajo. Este puede ser obtenido escribiendo a las siguientes direcciones Av. Instituto Politécnico Nacional No. 1310 Col. Nueva Tijuana, Tijuana, Baja California, México, correo electrónico de contacto: posgrado@citedi.mx. Si el permiso se otorga, el usuario deberá dar el agradecimiento correspondiente y citar la fuente del mismo.

Octavio Augusto García Alarcón.

### Dedicatoria

${\bf A}$  los sueños perdidos que motivaron este camino, y a los nuevos sueños que están por cumplirse...

#### Agradecimientos

Agradezco al CONACYT y al IPN por su apoyo durante el desarrollo de este trabajo.

Gracias a mi familia sanguínea, mi círculo dorado que siempre me ha apoyado en mi camino a pesar de todas las dificultades y nos hemos mantenido juntos en estos 4 años.

Gracias Ko. Sin tu amor, apoyo y consejos el camino hubiera sido más sinuoso y cansado.

Gracias a mis familias adoptivas en Tijuana y a todos los que me abrieron su casa y me dieron tiempo y amistad.

Gracias a mi asesor Javier Moreno, por ser mi guía académico pero sobre todo mi amigo.

Agradezco a mi comité tutorial por darme correcciones y ayudarme en el camino, principalmente al Dr. Victor Diaz y al Dr. Luis Aguilar los cuales aportaron consistencia y contundencia al trabajo.

Gracias a la gente del administrativo que respeta su trabajo y al estudiante y por la cual el camino se hizo menos pesado: Patty, Shamari, Sharith, Valderrama, Edith, Wence. Ojalá todos tomaran su trabajo con gusto como ustedes. Muchas gracias.

A mis amigos del Underwater & Co. por su amistad, apoyo, risas y sobre todo, sentido común. Son unos cracks...y debajo del agua también.

A mis brothers y sisters que han estado a lo largo del camino y siempre me han alentado: Cuevas, Monchiz, Nory, Galaviz, Ninel, Jorge Guzmán, Betty, Carlos Aguilar, Pacher, Eva, Ciencia, Rigus y Chanito.

A todos mis amigos y compañeros de CITEDI con los cuales compartí tiempo, espacio y amistad.

A Tijuana, la zona norte de mi corazón. De nuevo, gracias por cuidarme y quererme tanto.

#### Resumen

Un convertidor de potencia de C.D.-C.D., es un circuito electrónico de potencia que puede cambiar un nivel de corriente directa a otro de nivel de corriente directa. Tradicionalmente estos convertidores son diseñados sin considerar la saturación de la señal de control por lo que en casos prácticos se puede degradar el comportamiento deseado del convertidor por limitaciones físicas. La presenta tesis aborda el análisis, diseño e implementación de controladores para convertidores de potencia de C.D.-C.D. considerando la saturación de la señal de control. Se presenta un nuevo controlador saturado diseñado para realizar regulación del voltaje de salida en un convertidor boost implementando sin mediciones del voltaje de la fuente de entrada y la corriente del inductor. Un observador para el voltaje de la fuente de entrada y corriente de inductor fue implementado para este caso. También se presenta un nuevo controlador saturado diseñado para realizar regulación del voltaje de salida en un convertidor buck sin mediciones de la corriente del inductor. Un observador para estimar la corriente del inductor es implementado. En ambos casos, se presentan sus respectivos análisis de estabilidad y comparaciones experimentales con otros controladores de la literatura. Conclusiones finales son presentadas discutiendo el desempeño de los controladores presentados.

#### Abstract

A D.C.—D.C. power converter is a power electronics circuit that can change a direct current level to another direct current level. Traditionally this power converters are designed without considering the control signal saturation, this causes in practical cases the degradation of the desired performance of the power converter caused by physical limitations. This thesis work addresses with the analysis, design and implementation of D.C.—D.C. power converters considering the saturation of the control signal. A new saturated controller designed is presented to perform output voltage regulation in a boost power converter without measurements of the inductor current and the input source voltage. An observer for the inductor current and input source voltage is implemented. Also a new saturated controller designed to perform output voltage regulation in a buck power converter is presented implementing without inductor current measurements. An observer to estimate the inductor current is implemented. In both cases, their respective stability analysis and experimental comparison with other controllers of literature are presented. Final conclusions are presented discussing the performance of the presented controllers.

## Contenido

| 1. | $\operatorname{Intr}$ | oducción                                                                   | 1  |

|----|-----------------------|----------------------------------------------------------------------------|----|

|    | 1.1.                  | La electrónica de potencia                                                 | 1  |

|    | 1.2.                  | Convertidores de potencia                                                  | 2  |

|    |                       | 1.2.1. Convertidores de potencia por conmutación                           | 3  |

|    | 1.3.                  | Convertidores de potencia de C.D                                           | 3  |

|    | 1.4.                  | Revisión bibliográfica                                                     | 5  |

|    | 1.5.                  | Formulación del problema                                                   | 10 |

|    | 1.6.                  | Aportaciones                                                               | 11 |

|    | 1.7.                  | Objetivos                                                                  | 12 |

|    |                       | 1.7.1. Objetivo general                                                    | 12 |

|    |                       | 1.7.2. Objetivos específicos                                               | 12 |

|    | 1.8.                  | Contenido de la tesis                                                      | 12 |

| 2. | Fun                   | damentos y modelado de convertidores de C.DC.D.                            | 13 |

|    | 2.1.                  | Modos de conducción                                                        | 13 |

|    |                       | 2.1.1. Modo de conducción acotado                                          | 14 |

|    |                       | 2.1.2. Modo de conducción discontinuo                                      | 14 |

|    |                       | 2.1.3. Modo de conducción continua                                         | 15 |

|    | 2.2.                  | Modelado por funciones de conmutación de un convertidor buck $\dots \dots$ | 16 |

|    | 2.3.                  | Modelado por funciones de conmutación de un convertidor boost              | 19 |

|    | 2.4.                  | Definiciones de potencia y energía                                         | 21 |

|    |                       | 2.4.1. La potencia y energía en un convertidor de C.D.–C.D. como factores  |    |

|    |                       | para determinar las ganancias de un controlador                            | 22 |

| 3. | Con                   | trol de un convertidor boost con entrada restringida.                      | 27 |

|    | 3.1.                  | Objetivos de control                                                       | 27 |

|    | 3.2.                  | Contribuciones                                                             | 28 |

|    | 3.3.                  | Modelado del convertidor                                                   | 28 |

iv CONTENIDO

|           | 3.4.  | Controlador propuesto                                                        | 30         |

|-----------|-------|------------------------------------------------------------------------------|------------|

|           |       | 3.4.1. Controlador propuesto para voltaje de entrada y corriente de induc-   |            |

|           |       | tor desconocidos                                                             | 33         |

|           |       | 3.4.2. Corolario                                                             | 36         |

|           | 3.5.  | Resultados experimentales                                                    | 37         |

|           | 3.6.  | Conclusiones                                                                 | 42         |

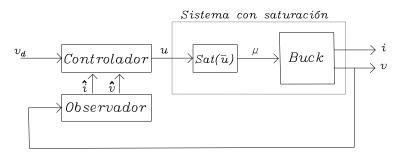

| 4.        | Con   | trol saturado con observador de corriente para un convertidor buck.          | 43         |

|           | 4.1.  | Objetivos de control                                                         | 44         |

|           | 4.2.  | Contribuciones                                                               | 44         |

|           | 4.3.  | Modelado del convertidor buck                                                | 44         |

|           | 4.4.  | Diseño del controlador                                                       | 45         |

|           | 4.5.  | Observador propuesto                                                         | 48         |

|           | 4.6.  | Control propuesto + observador                                               | 50         |

|           |       | 4.6.1. Corolario                                                             | 55         |

|           | 4.7.  | Experimentos                                                                 | 57         |

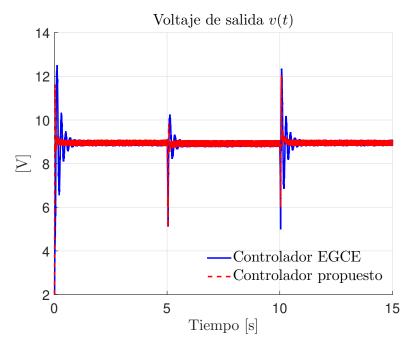

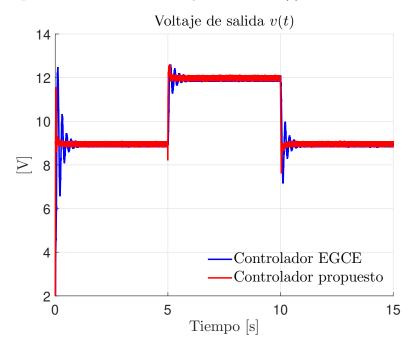

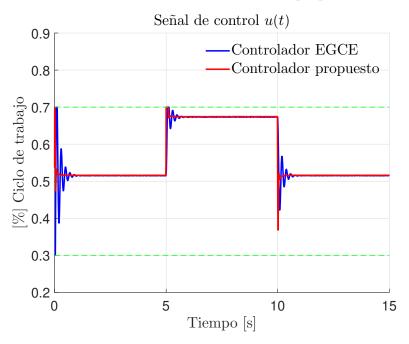

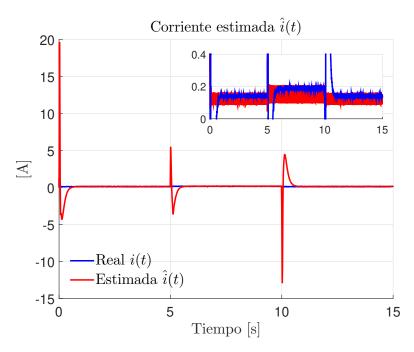

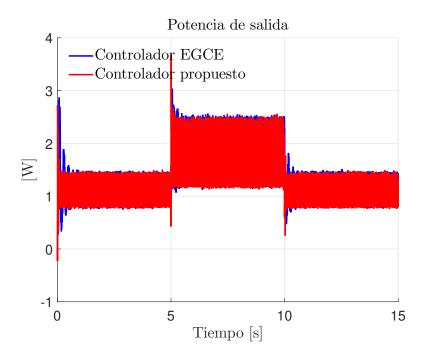

|           |       | 4.7.1. Control del voltaje de salida fijo con cambio en la fuente de voltaje | 58         |

|           |       | 4.7.2. Cambio del voltaje deseado con fuente de voltaje fija                 | 63         |

|           |       | 4.7.3. Regulación del voltaje de salida con cambio en la carga               | 69         |

|           | 4.8.  | Conclusiones                                                                 | 73         |

| <b>5.</b> | Con   | aclusiones.                                                                  | <b>7</b> 5 |

|           |       | 5.0.1. Trabajo futuro                                                        | 76         |

| Re        | efere | ncias                                                                        | 98         |

## Capítulo 1

#### Introducción

#### 1.1. La electrónica de potencia

La energía eléctrica es el músculo de la industria mientras que la electrónica de potencia moderna hace de esta su utilización más inteligente y eficiente [1]. La energía eléctrica se utiliza en prácticamente todas las áreas de la sociedad, por lo tanto un uso eficiente de la energía se ha convertido en algo fundamental y su gestión es un punto esencial en el diseño de cualquier sistema en todos los campos de la ingeniería [2]. El objetivo de la electrónica de potencia es mejorar la calidad y utilización de la energía eléctrica, la cual es usada en diferentes niveles según los dispositivos disponibles, procesos y las tecnologías en cuestión [3]. En la electrónica de potencia se combinan el estudio de la potencia, la electrónica y el control de la siguiente forma:

- La potencia tiene que ver con el equipo estático y rotatorio para la generación, transmisión y distribución de energía.

- La electrónica tiene que ver con los dispositivos y circuitos de estado sólido para el procesamiento de señales que cumplan con los objetivos deseados en el control.

- El control tiene que ver con las características de estado estable y dinámicas de lazo cerrado de los convertidores de potencia y su potencia eléctrica [3], [4], [5].

La electrónica de potencia ha revolucionado el concepto de control de la potencia en la conversión de energía [3], entonces electrónica de potencia se puede definir como "las aplicaciones de la electrónica para el control y conversión de la energía eléctrica basándose principalmente en la conmutación de dispositivos semiconductores de potencia". En resumen, la electrónica de potencia es una tecnología habilitadora que reúne tres

tecnologías fundamentales: tecnología de dispositivos de semiconductores, tecnología de conversión de energía y tecnología de control de energía [6].

#### 1.2. Convertidores de potencia

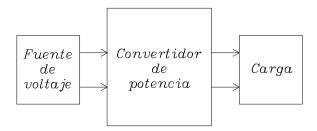

De manera general para poder ocomprender que es un convertidor de potencia, primero hay que pensar en dos cosas básicas: una carga y una fuente de voltaje. La fuente de voltaje provee energía que puede ser voltaje de corriente directa (C.D.) o de corriente alterna (C.A.) y la carga es un elemento que consume el voltaje. Por su parte el bloque intermedio entre estos dos elementos es el convertidor de potencia el cual recibe el voltaje de la fuente y lo transforma, regula y entrega a la carga (Figura 1.1).

Figura 1.1: Diagrama general de un convertidor de potencia.

Hablando del impacto que ha tenido la electrónica de potencia sobre el área de control se puede mencionar que el desarrollo tanto de la tecnología de semiconductores de potencia como de microprocesadores y de computadoras en general ha logrado un gran impacto sobre las estrategias de control para los convertidores de potencia [2], [3], [4], [7]; lo cual abre la posibilidad a regular mejor la potencia eléctrica entregada, mejorar el rendimiento de la carga que consume esta potencia y posibles ahorros de energía proveniente de la fuente.

En los últimos años, los convertidores de conmutación se han vuelto muy populares debido a los recientes avances en la tecnología de semiconductores. Hoy en día, los dispositivos de conmutación están disponibles con velocidades de conmutación muy altas y capacidades de manejo de potencia muy altas. Es posible diseñar fuentes de alimentación de modo conmutado con una eficiencia superior al 90 % con bajo costo y tamaño relativamente pequeño y peso ligero [8].

#### 1.2.1. Convertidores de potencia por conmutación

Para lograr el control de la potencia eléctrica, es necesaria la conversión de esta y que las características de conmutación de los dispositivos de potencia permitan esas conversiones.

Como se menciona en [1], [3], [4], [8] y [9], los circuitos conversores de potencia se pueden clasificar en términos de su descripción funcional y pueden desempeñar una o más de las siguientes funciones de conversión:

- 1. Rectificación (C.A.-C.D.).

- 2. Inversión (C.D.–C.A.).

- 3. Ciclo-conversión (C.A.-C.A. a diferentes frecuencias) ó controladores de C.A. (C.A.-C.A. a las mismas frecuencias).

- 4. Conversión (C.D.-C.D.).

El presente trabajo se centra únicamente en convertidores de C.D.-C.D. y a partir de este punto podrán ser referidos simplemente como convertidores de C.D.

#### 1.3. Convertidores de potencia de C.D.

Un convertidor de C.D. se puede considerar como el equivalente a un transformador de C.A., con una relación de vueltas que varía en forma continua y que al igual que su análogo, se puede usar para aumentar o disminuir el voltaje de una fuente [3], [10].

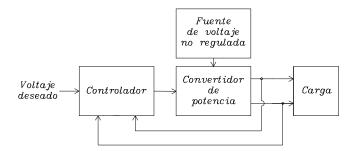

Figura 1.2: Diagrama general de control de un convertidor de potencia de C.D.

Los dispositivos de conmutación que se utilizan para procesar la energía de la entrada a la salida son semiconductores usados en configuración de interruptores. Como la entrada es de C.D. y proviene de una etapa posterior al filtrado, estos dispositivos normalmente

operan a frecuencias mucho más altas que la frecuencia de la línea, llegando a unos pocos cientos de kHz. Esta es la razón por la que estos circuitos convertidores de potencia se conocen como convertidores o reguladores de conmutación C.D.—C.D. de alta frecuencia. El término regulador se usa ya que la principal aplicación comercial del circuito es en sistemas que requieren un voltaje de salida de C.D. estable y regulado. Dependiendo de si se usa o no un transformador de salida, los convertidores de conmutación C.D.—C.D. de alta frecuencia se clasifican como aislados o no aislados [8].

Los convertidores C.D.—C.D. se utilizan en circuitos electrónicos de potencia para convertir un voltaje C.D. no regulado a un voltaje de salida C.D. regulado o variable. Estos circuitos dominan la industria de las fuentes de alimentación, como las fuentes de alimentación de modo conmutado (switched mode power supplies ó SMPS). En las aplicaciones de accionamiento de tracción de alta potencia, los convertidores C.D.—C.D. se conocen como interruptores [8]. Se usan también para el control de motores de C.D. que pueden ser usados como tracción en automóviles eléctricos, tranvías, grúas marinas, montacargas y elevadores [11], [12], [13], [14]. Proporcionan un control uniforme de aceleración, gran eficiencia y rápida respuesta. Se pueden usar en el frenado regenerativo de motores de C.D. para regresar la energía a la fuente, y esa propiedad permite ahorros de la misma en los sistemas de transporte que tienen frenados frecuentes. Se utilizan también en los reguladores de voltaje de C.D. y se usan en conjunto con un inductor para generar una corriente, en especial para el inversor de una fuente de corriente [2], [3], [4], [15]. Más recientemente su uso ha incrementado aún más en energías renovables y microredes [16], [17], [18], [19].

Generalmente las entradas de estos convertidores son un voltaje no regulado el cual es obtenido por la rectificación de una línea de voltaje de corriente alterna o por una batería; por lo tanto es normal una fluctuación debido a cambios en las magnitudes del voltaje de la línea eléctrica o de los químicos y materiales en las baterías (figura 1.2). Los convertidores de C.D. utilizan un modo de conmutación el cual es usado para convertir una entrada no regulada de voltaje en una salida de voltaje regulado al nivel deseado. Como mencionan [4] y [8], los convertidores de potencia de C.D.–C.D. se pueden clasificar en:

- Convertidor elevador (boost).

- Convertidor reductor (buck).

- Convertidor reductor-elevador (buck-boost).

- Convertidor Ćuk.

- Convertidor SEPIC.

- Convertidor ZETA.

De los cuales, los convertidores buck y boost son las topologías básicas mientras que los otros son combinaciones o variantes de estos. El objetivo principal de estos convertidores es controlar el voltaje de salida para ser equivalente a un nivel deseado (regulación) aunque el voltaje de entrada y/o la carga de salida puedan variar. Para lograrlo, en estos convertidores se requiere una o más conmutaciones para transformar corriente directa de un nivel a otro. El nivel de salida es controlado por esta conmutación de estados y su tiempo de duración. Comúnmente se requiere una modulación por ancho de pulso PWM (pulse width modulation por sus siglas en inglés) donde se requiere una frecuencia constante y lo que varía es el tiempo de duración del interruptor en modo encendido. A esta variación en el tiempo de trabajo o encendido del interruptor se le conoce comúnmente como porcentaje de ciclo de trabajo (duty cycle).

El presente trabajo se centra unicamente en el control de convertidores de C.D.-C.D. boost y buck.

#### 1.4. Revisión bibliográfica

A continuación se muestra una revisión bibliográfica de forma cronológica en el diseño de convertidores de potencia de C.D.:

- Middlebrook y Ćuk (1976) inician el modelado de convertidores de potencia C.D. regulados por interruptores [20].

- R. Ortega et al. (1998) estudian los convertidores de potencia como sistemas Euler-Lagrange y proponen controladores basados en pasividad [21].

- En 2000, Lyshevski [22] propuso modelos matemáticos de cuarto orden para algunas combinaciones de convertidores de potencia acoplados a un motor de C.D. y, adicionalmente, diseñó controladores proporcionales-integrales (PI) clásicos para la regulación de la velocidad angular del motor.

- D. Karagiannis et. al (2003) presentan resultados de regulación de voltaje únicamente mediciones del voltaje de salida desconociendo el voltaje de entrada [23].

- En 2004, Linares-Flores y Sira-Ramírez [24] presentaron un diseño para controladores de velocidad angular suave para un sistema convertidor-motor, en el que la

efectividad de los controladores propuestos se verificó solo mediante simulaciones numéricas.

- En [25], Linares-Flores (2004) presentó un arrancador suave, basado en el enfoque de planitud diferencial (differential flatnes), para regular la velocidad de un motor de C.D. alimentado por un convertidor Buck. Este motor de arranque se diseñó a través de un modelo de segundo orden simplificado, que se obtiene al considerar que la inductancia del motor y la corriente del condensador en el convertidor son insignificantes.

- En [26], Linares-Flores (2004) se introdujo un control, implementado a través de un modulador  $\sigma \Delta$ , para la tarea de seguimiento de la trayectoria de la velocidad angular, explotando las características del sistema combinado. Para lograr esto, emplearon el modelo matemático obtenido en [24].

- H. Sira-Ramirez y Silva Ortigoza (2006) introducen el modelado de circuitos de potencia conmutados como sistemas dinámicos controlados [10].

- En 2006, Linares-Flores [27] presentaron un controlador para la tarea de seguimiento de la trayectoria de la velocidad angular, basada en la planitud diferencial y un modelo de cuarto orden, para un sistema convertidor de potencia/motor. El controlador se implementó experimentalmente mediante el uso del PWM a través de tarjetas de adquisición de datos. Sin embargo, en ambas obras, no se incluyó ninguna validación experimental cuando aparecieron incertidumbres paramétricas en el sistema.

- En 2006, El Fadil y Giri [28], para atacar el problema de control de velocidad de un motor de corriente directa con un convertidor Buck, diseñaron un regulador basado en técnica de retroceso y un modelo de cuarto orden. Además, propusieron versiones adaptativas, no-adaptativas de los controladores. A través de simulaciones numéricas donde se usó el PWM, se mostró que la versión adaptable trata mejor con cambios de par de carga. Sin embargo, ni referencias suaves ni las incertidumbres paramétricas del sistema global eran considerados.

- Spinetti et al. (2009) presentan un análisis de estabilidad de un convertidor boost con un control basado en Lyapunov [29].

- Olalla et al. (2009) proponen un controlador  $H_{\infty}$  aplicado a convertidores C.D. con entradas saturadas [30].

- Ahmad et al. (2010) [31], presenta a través de simulaciones numéricas, una evaluación comparativa del rendimiento de un controlador PI de tipo lógica difusa y controladores LQR (linear quadratic regulator por sus siglas en inglés) para la tarea de seguimiento de la trayectoria de la velocidad angular de un motor de corriente continua alimentado por un convertidor Buck.

- En 2011, Sureshkumar y Ganeshkumar [32] compararon para el mismo sistema, a través de simulaciones numéricas, el rendimiento de ambos controladores PI y backstepping, asociados con la regulación de la velocidad angular del sistema mencionado anteriormente.

- Wu y Liu (2011) presentan controladores no lineales aplicados a convertidores C.D.

[33].

- Tani y Camara, B.(2012) Dakyo presentan convertidores de potencia aplicados a vehículos híbridos [34].

- En contraste con los trabajos previos, en 2012 Bingol y Pacaci [35] presentaron un laboratorio virtual, para emular la tarea de velocidad angular, que incluido un conjunto de entrenamientos en un controlador de redes neuronales para un motor de corriente continua alimentado por un convertidor Buck. Este conjunto permite que los parámetros del motor de corriente continua y del controlador se puedan cambiar, y permite observar la reacción del sistema bajo varias condiciones operacionales para ser monitoreadas por medios de una interfaz gráfica de usuario.

- En 2012 Chen, Ren, y Oliver, presentaron un controlador adaptativo por redes neuronales [36]. Sin embargo, su esquema al estar basado en la inversión de la función de saturación, sólo puede ser alcanzado localmente.

- Guzman-Guemez y Moreno-Valenzuela (2013) presentan un control saturado de un convertidor boost [37].

- En 2013, Sira-Ramírez y Oliver-Salazar [38] describieron una ley de control robusto basada en el control de rechazo de perturbaciones activas y control basado en la planeidad, teniendo en cuenta una carga desconocida variable en el tiempo para dos combinaciones de convertidores Buck y motores de corriente continua. Simulaciones numéricas mostraron la solidez de esta técnica para el control de velocidad angular del eje del motor.

- En 2013, Silva-Ortigoza et al. [39] introdujeron un control de dos etapas basado en planitud diferencial para el control de velocidad angular sin tomar en cuenta las mediciones de velocidad del sistema de convertidor-motor. Se mostró, a través de simulaciones numéricas que incluían un modulador Σ Δ, que la propuesta del esquema de control efectivamente proporciona robustez al seguimiento cuando las incertidumbres paramétricas relacionadas con el sistema aparecen. Además, importantes contribuciones relacionadas con la conexión de otros convertidores de potencia C.D. y motores de C.D. se reportaron en [27], [40], [41].

- Alexandridis y Konstantopoulos (2014) presentan un control P.I. de velocidad en un motor de C.D. excitado en serie. [42]

- Guzman-Guemez y Moreno-Valenzuela (2015) presentan evaluaciones experimentales en reguladores de voltaje para un convertidor boost saturado [43].

- Bonanno, Capizzi y Lo Sciuto (2015) presentan convertidores de potencia aplicados a sistemas fotovoltaicos [44].

- Silva-Ortigoza et al. (2015) presentan una aplicación del convertidor Buck como arrancador suave para un motor de C.D. basado en control jerárquico [45].

- Du, Lai, y Liu (2015), presentaron un método de control para obtener corriente constante en un convertidor boost [46].

- Benzaouia et. al (2016) presentan un método para colocación de polos con control saturado en un convertidor buck implementado en "hardware in the loop" [47]

- Konstantopoulos y Zhong (2016) presentan simulaciones de un controlador no lineal con capacidad limitadora de corriente, donde la estrategia de control ofrece una propiedad de protección inherente ya que la potencia del convertidor es limitada [48].

- En [49] Silva Ortigoza et. al (2017) presentan el modelado y la validación experimental de una nueva topología para el convertidor Buck. El objetivo principal de esta topología es lograr una rotación bidireccional en el eje del motor de C.D. mediante el uso de un convertidor de potencia C.D.-C.D. Como resultado de aplicar las leyes de corriente y voltaje de Kirchhoff, se obtiene el modelo matemático del sistema. Además, se presenta un análisis en estado estable del sistema. Mientras, la generación de la trayectoria de referencia asociada a los estados y controles del sistema (expresada en términos del convertidor de voltaje y la velocidad angular

del motor) se realiza a través de planiedad diferencial, que permite un control de seguimiento de trayectoria en bucle abierto. La validación experimental del modelo presentado aquí se lleva a cabo por medio de Matlab-Simulink, ControlDesk, y un DS1104 de dSPACE. Los resultados experimentales confirman la validez del modelo matemático, para el caso general, es decir, el seguimiento de trayectoria variable en el tiempo y no solo el caso de trayectorias constantes.

- Hyuk y Young (2017) presentan un controlador en cascada con observadores integrales—proporcionales para mantener el rendimiento deseable de regulación del voltaje de salida para un convertidor C.D.—C.D. sujeto a cambios en la carga, incertidumbres paramétricas y variaciones de voltaje de voltaje a la entrada [50].

- Más recientemente, Ma et al. (2018) presentan un controlador por modos deslizantes de segundo orden para un convertidor reductor [51]

- En [52] (2018) se presenta un controlador por retroalimentación con retardo de tiempo para regular el voltaje de salida de un convertidor reductor.

- En trabajo trata sobre el diseño de un esquema de control robusto y descentralizado basado en la pasividad para regular el voltaje de una microrred de CC a través de convertidores de refuerzo.

- M. Cucuzzella et al. (2019) presentan el diseño de un esquema de control robusto y descentralizado basado en la pasividad para regular el voltaje de una micro-red de C.D. a usando convertidores boost [53].

Como puede observarse en la revisión bibliográfica, el tema de convertidores de potencia de C.D.— C.D.sido investigado ampliamente y ha tenido una gran una evolución que sigue siendo un nicho para la investigación, análisis y diseño de nuevos controladores que tengan mejor desempeño con buenas características.

En esta revisión se pueden visualizar tres campos de estudio en la investigación de control para convertidores de potencia de C.D.:

- controladores para convertidores C.D.-C.D.

- controladores para convertidores C.D.-C.D. en cascada con otro sistema

- controladores saturados para convertidores C.D.-C.D.

donde el tema menos estudiado es la saturación en controladores para convertidores de potencia. El presente trabajo aporta estudios de este tema.

#### 1.5. Formulación del problema

La mayoría de las aplicaciones que requieren regulación de corriente directa a corriente directa (C.D.-C.D.) usan un convertidor de potencia [6], por lo que existe una gran demanda en el mercado por convertidores más eficientes. Los convertidores de potencia son susceptibles a presentar comportamientos no lineales, lo cual no es deseable y debe ser evitado porque es perjudicial para su correcta y normal operación y puede llevar a inestabilidades [54]. Por lo tanto, refinar y mejorar las técnicas existentes de análisis puede llevar a un mejor desempeño de los convertidores de potencia [6].

Por otro lado, el ciclo de trabajo es la entrada de control del convertidor de potencia, el cual toma de manera ideal los valores entre cero y uno. De manera usual, la acción de control puede estar fuera de los límites admisibles de la señal PWM, lo cual es considerado como una saturación. Comúnmente esto no es tomado en cuenta para el análisis del sistema de control [55]. El fenómeno de saturación de entrada es una de las no linealidades más comúnes en todos los sistemas físicos y es raramente considerada en el análisis y diseño de controladores para convertidores de potencia [56]. La razón es que la complejidad del análisis de estabilidad del sistema de lazo cerrado se incrementa considerablemente. Adicionalmente al problema de la saturación, las mediciones de corriente son ruidosas y el conocimiento impreciso del voltaje de alimentación complica más el problema de regulación de voltaje de salida del convertidor. Se puede observar también que el problema sobre los convertidores de potencia en la investigación de control no lineal con entrada saturada, da la posibilidad de mejorar el desempeño del convertidor para regular el voltaje a su salida, incluso el usar esta regulación de voltaje para controlar otro sistema en cascada [15], [37], [43].

Entonces puede plantearse la problemática de manera general y específica:

#### Problemática general

Regulación del voltaje de salida en convertidores de potencia de C.D.-C.D.

#### Problemática específica

- Se necesita optimizar los controladores para mejorar la regulación del voltaje de salida de los convertidores de potencia de C.D.-C.D.

- Se necesita diseñar controladores no lineales para mejorar la regulación de voltaje de los convertidores de C.D.-C.D.

1.6 Aportaciones 11

Se necesita mejorar el desempeño de los controladores de convertidores de potencia de C.D.-C.D., principalmente a incertidumbres en la fuente de voltaje de entrada ó a mediciones ruidosas de la corriente del inductor.

Con esta problemática presentada se formula la siguiente pregunta:

¿Cómo mejorar el desempeño de regulación de voltaje de salida en un convertidor de voltaje C.D.-C.D. a través de un controlador?

#### Hipótesis

La implementación de controladores no lineales que contemplen la saturación de la señal de control pueden mejorar el desempeño de los convertidores de potencia de C.D.-C.D. tanto en la regulación del voltaje a la salida como a incertidumbres en la fuente de voltaje de entrada ó a mediciones ruidosas de la corriente del inductor.

#### 1.6. Aportaciones

El tema de control aplicado a convertidores de potencia no es nuevo, pero dado el avance de la ciencia, la tecnología y la sociedad en general, cada vez se ha hecho más importante y necesario poder regular la energía de diversos sistemas utilizados comúnmente de manera más eficiente, por lo cual el estudio de controladores de convertidores de potencia C.D.—C.D. es un tema moderno, actual y de mucha importancia. La aportación de este trabajo es diseñar controladores saturados para convertidores de potencia de C.D.—C.D. Si a esto se le suma que pocos han sido los estudios de estos controladores en la literatura revisada tomando en cuenta la entrada saturada, la propuesta se vuelve más original e importante. Adicional a estos puntos, pocos trabajos han presentado experimentos que validen de manera contundente los análisis. Por lo que las principales aportaciones de este trabajo son:

- La introducción y diseño de un nuevo controlador para un convertidor de potencia boost con entrada saturada implementando un observador para el voltaje de la fuente de entrada y la corriente de inductor para la regulación del voltaje de salida.

- La introducción de un nuevo controlador para un convertidor de potencia buck con entrada saturada implementando un observador para la corriente del inductor para la regulación del voltaje de salida.

Realización de experimentos en los dos casos anteriores comparando resultados con otros controladores de la literatura.

Lo cual tiene más contundencia en la aportación del presente trabajo.

#### 1.7. Objetivos

#### 1.7.1. Objetivo general

Analizar, proponer e implementar en tiempo real controladores para convertidores de potencia con el propósito de satisfacer la regulación del voltaje de salida.

#### 1.7.2. Objetivos específicos

- Analizar, diseñar y construir convertidores de potencia C.D.-C.D.

- Estudiar, diseñar e implementar controladores de convertidores de potencia C.D.—C.D.

- Estudiar, proponer, diseñar e implementar controladores de convertidores de potencia C.D.-C.D. con ciclo de trabajo saturado.

#### 1.8. Contenido de la tesis

El presente trabajo se encuentra organizado de la siguiente forma:

El capítulo 2 presenta los fundamentos y modelado de convertidores de C.D.-C.D. por funciones de conmutación y establece las reglas en como son estudiados los convertidores de C.D. en este trabajo.

El capítulo 3 presenta un nuevo controlador saturado diseñado para realizar regulación del voltaje de salida en un convertidor boost implementando un observador para el voltaje de la fuente de entrada y corriente de inductor, su respectivo análisis de estabilidad y la comparación experimental con otro controlador de la literatura.

El capítulo 4 presenta un nuevo controlador saturado diseñado para realizar regulación del voltaje de salida en un convertidor buck implementando un observador para la corriente del inductor, su respectivo análisis de estabilidad y la comparación experimental con otro controlador de la literatura.

Finalmente en el capítulo 5 se presentan las conclusiones de este trabajo de tesis así como el posible trabajo futuro del mismo.

## Capítulo 2

# Fundamentos y modelado de convertidores de C.D.-C.D.

Para poder controlar un convertidor de potencia de C.D.—C.D. de manera general se necesita conocer lo siguiente:

- el voltaje de entrada,

- el voltaje de salida,

- la corriente del inductor.

Este último elemento es clave para el funcionamiento de los convertidores de potencia de C.D., por lo que conocer a fondo su comportamiento es de gran ayuda para entender el funcionamiento de cualquier convertidor de C.D.

#### 2.1. Modos de conducción.

En los convertidores de C.D. el uso del inductor es importante pues su operación (la cual consiste en la carga de campo magnético y transferencia de este como corriente eléctrica) depende de la conmutación de los semiconductores, lo que lleva a una transferencia de energía del inductor a la resistencia de carga pasando por el capacitor.

Un inductor es un alambre o hilo de cobre esmaltado enrollado. Este enrollado es lo que comúnmente se llama devanado del inductor y corresponde al número de vueltas que ayudan a producir el campo magnético inducido por el paso de la corriente. Los inductores pueden contener diferentes tipos de núcleo, aunque para este estudio se utilizan inductores con núcleo de aire.

$$\xrightarrow{+}^{v_L} -$$

$$i(t)$$

Figura 2.1: Símbolo de un inductor.

El voltaje  $v_L$  a través del inductor L se calcula como

$$v_L = L \frac{di}{dt},\tag{2.1}$$

donde i(t) es la corriente que circula através del inductor. El sentido de la corriente eléctrica es definido al momento de modelar el circuito. La figura 2.1 muestra el símbolo de un inductor con el sentido de la corriente estándar. El comportamiento de la corriente del inductor puede variar dependiendo ciertas condiciones físicas y la aplicación.

Cabe mencionar que el análisis de la corriente del inductor en los diversos modos de conducción, es en estado estable. Los diferentes modos de conducción de la corriente en un inductor se describen a continuación.

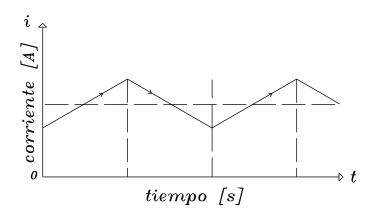

#### 2.1.1. Modo de conducción acotado

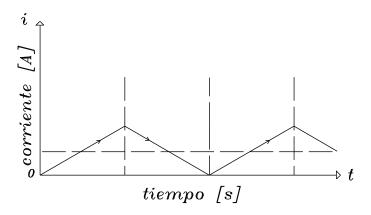

Nombrado BCM, bounded conduction mode por sus siglas en inglés. Cuando la corriente toca cero por un instante sin bajar de este valor y subiendo inmediatamente, se dice que el inductor está trabajando en modo de conducción acotado (Figura 2.2).

#### 2.1.2. Modo de conducción discontinuo

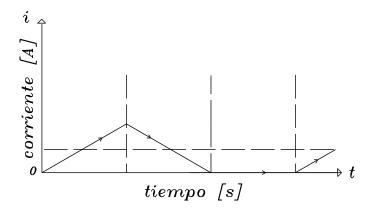

Nombrado DCM, discontinuous conduction mode por sus siglas en inglés. A diferencia del modo de conducción acotado, el modo de conducción discontinuo se da cuando algunos valores de corriente a través del inductor  $i_L$  permanecen en cero durante algún tiempo considerable y después sube (Figura 2.3).

Figura 2.2: Corriente del inductor  $i_L$  en modo de conducción acotado.

**Figura 2.3:** Corriente del inductor  $i_L$  en modo de conducción discontinua.

#### 2.1.3. Modo de conducción continua

Nombrado CCM, continuous conduction mode por sus siglas en inglés. Durante el modo de conducción continua, la corriente del inductor en la transferencia de energía nunca alcanza el valor cero (Figura 2.4). La ventajas del CCM son las siguientes:

- La ganancia de voltaje no es dependiente de la carga.

- La corriente de entrada es continua y no pulsante.

- El componente de rizo u ondulación de la corriente del inductor es más bajo que el componente promedio.

- Se puede lograr más eficiencia en comparación al DCM.

Este trabajo se centra en el estudio de convertidores de potencia C.D.–C.D. en modo de conducción continua.

Figura 2.4: Corriente del inductor  $i_L$  en modo de conducción continua.

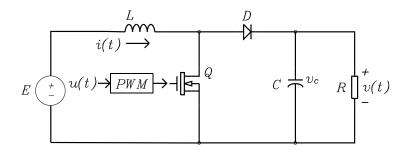

Figura 2.5: Diagrama estándar del convertidor reductor o buck.

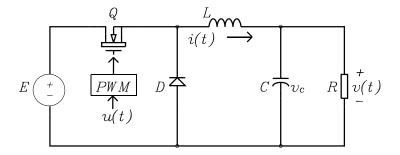

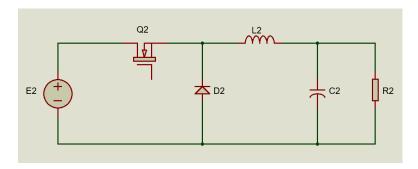

## 2.2. Modelado por funciones de conmutación de un convertidor buck

El convertidor reductor también conocido como buck, reduce el voltaje de entrada de corriente directa de cierto valor a un voltaje de salida de corriente directa menor al del voltaje de entrada [57], [58]. El circuito estándar o general es el mostrado en la figura 2.5. Los componentes que forman al convertidor reductor son

- $\blacksquare$  La fuente de alimentación E.

- lacktriangle El diodo D y el transistor Q que son los elementos semiconductores de conmutación.

- La señal de control u(t) la cual es una señal analógica que mediante un circuito es convertida en una señal de modulado de ancho de pulso (PWM).

- $\blacksquare$  El inductor L.

- $\blacksquare$  El capacitor C.

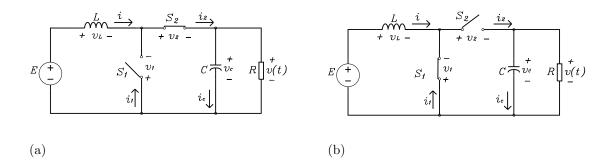

**Figura 2.6:** Circuito equivalente del convertidor buck en sus dos estados de conmutación. (a) Estado de conmutación  $S_1 = 0$ ,  $S_2 = 1$ , (b) Estado de conmutación  $S_1 = 1$ ,  $S_2 = 0$

Tabla 2.1: Tabla de conmutación del convertidor reductor.

| $S_1$ | $S_2$ | $i_1$ | $i_2$ | $v_1$ | $v_2$ |

|-------|-------|-------|-------|-------|-------|

| 0     | 1     | 0     | i     | E     | 0     |

| 1     | 0     | i     | 0     | 0     | -E    |

La carga R que aunque no forma parte del convertidor, se integra como parte del modelo.

El encendido y apagado a cierta frecuencia de conmutación del transistor Q es la base del funcionamiento del convertidor. Debido a su conexión, el diodo D se polariza directamente al estar apagado el transistor Q y se polariza inversamente al estar encendido el transistor Q, es decir, el funcionamiento de D y Q es complementario.

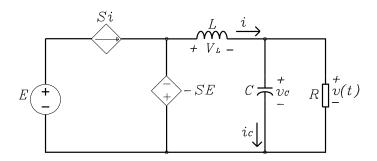

Establecido lo anterior, se redibuja el diagrama del convertidor reductor con los semiconductores representados como interruptores, donde las polaridades de los voltajes y corrientes son establecidos. El transistor Q es sustituido por la variable S1 y el diodo D es sustituido por la varible S2, y en los dos casos, sus símbolos sustituidos por interruptores que funcionan de manera complementaria, como puede observarse en la figura 2.6. Posteriormente se realiza la tabla de conmutación donde mediante el análisis del circuito en cada conmutación se definen los estados mostrados en la tabla 2.1.

Sustituyendo la variable  $S_1$  por una única señal de control conmutada S, y usando los valores de la tabla 2.1, se obtienen las ecuaciones (2.2)–(2.3):

$$i_1 = Si, (2.2)$$

$$V_2 = -SE, (2.3)$$

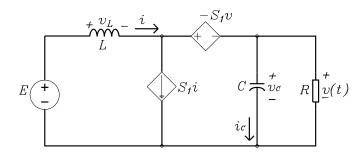

Figura 2.7: Circuito equivalente con fuentes dependientes del convertidor reductor.

las cuales representan una fuente de corriente dependiente y una fuente de voltaje dependiente respectivamente.

Usando las ecuaciones (2.2)–(2.3), se redibuja el circuito del convertidor como se muestra en la figura 2.7. Del circuito equivalente mostrado en la figura 2.7, se realiza el análisis mediante leves de Kirchoff, resultando

$$\frac{di}{dt} = -\frac{1}{L}v + \frac{1}{L}SE, \tag{2.4}$$

$$\frac{di}{dt} = -\frac{1}{L}v + \frac{1}{L}SE,$$

$$\frac{dv}{dt} = \frac{1}{C}i - \frac{1}{RV}v,$$

(2.4)

lo que describe la dinámica de la corriente del inductor L y del voltaje del capacitor Cal conmutarse la señal de control S. Las ecuaciones (2.4)–(2.5) representan el modelo del convertidor buck comúnmente llamado modelo de conmutación y donde se hace énfasis en la naturaleza binaria de la posición del interruptor S usando la relación  $S \in 0, 1$ .

Como se mencionó en la sección anterior, este análisis se realiza asumiendo el modo de conducción continua, y el sistema en estado estable. Estas suposiciones definen el comportamiento del voltaje v(t) y la corriente i(t) como variables promediadas y los parámetros C y L como constantes, por lo que el modelo promediado finalmente queda representado de manera similar al modelo (2.4)–(2.5), pero renombrando la señal de control S como u, la cual es una función suficientemente suave que toma valores en el intervalo [0,1]. Finalmente el modelo del convertidor reductor queda definido como

$$L\frac{di}{dt} = -v + uE, (2.6)$$

$$L\frac{di}{dt} = -v + uE, \qquad (2.6)$$

$$C\frac{dv}{dt} = i - \frac{v}{R}. \qquad (2.7)$$

Para más referencias del modelo promediado consultar [3], [10], [58].

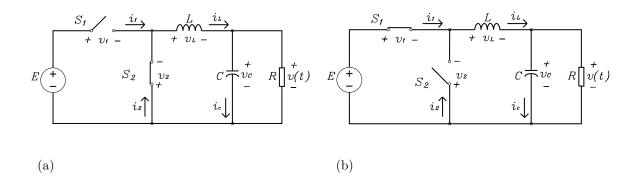

## 2.3. Modelado por funciones de conmutación de un convertidor boost

El convertidor boost, también conocido como convertidor elevador, produce un voltaje de salida igual o mayor que su voltaje de alimentación de entrada aunque su corriente de salida es menor [58]. Su aplicación normalmente es en fuentes de voltaje reguladas de C.D., en el control de velocidad de motores y en energías renovables.

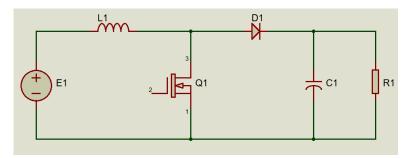

Figura 2.8: Diagrama estándar del convertidor elevador o boost.

El circuito del convertidor boost es presentado en la figura 2.8, donde puede observarse los siguientes componentes que lo conforman:

- $\blacksquare$  La fuente de alimentación E.

- El diodo D y el transistor Q que son los elementos semiconductores de conmutación.

- La señal de control u(t) la cual es una señal analógica que mediante un circuito es convertida en una señal de modulado de ancho de pulso (PWM).

- $\blacksquare$  El inductor L.

- $\blacksquare$  El capacitor C.

- La carga R que, aunque no forma parte del convertidor, se integra como parte del modelo.

Al igual que en los demás convertidores, en el convertidor boost el encendido y apagado a una frecuencia de conmutación dada en el transistor Q es la base del funcionamiento del convertidor. El funcionamiento de D y Q es complementario.

Como se explicó en la sección anterior, el procedimiento de modelado se inicia dibujando el circuito equivalente del convertidor utilizando interruptores en lugar de los dispositivos semiconductores, donde las polaridades de los voltajes y las direcciones de las

**Figura 2.9:** Circuito equivalente del convertidor elevador o boost en sus dos estados de conmutación. (a) Estado de conmutación  $S_1 = 0$ ,  $S_2 = 1$ , (b) Estado de conmutación  $S_1 = 1$ ,  $S_2 = 0$

Tabla 2.2: Tabla de conmutación del convertidor elevador boost.

| $S_1$ | $S_2$ | $i_1$ | $i_2$ | $v_1$ | $v_2$ |

|-------|-------|-------|-------|-------|-------|

| 0     | 1     | 0     | i     | v     | 0     |

| 1     | 0     | i     | 0     | 0     | -v    |

corrientes en cada elemento del circuito son establecidas al momento de hacer el análisis. El circuito equivalente en sus dos estados de conmutación es mostrado en la figura 2.9.

A continuación, se sustituyen los componentes semiconductores por las siguientes funciones de conmutación:

$$Q = S_1,$$

$$D = S_2.$$

donde  $S_1$  y  $S_2$  son funciones binarias y complementarias. Posteriormente se realiza la tabla de conmutación donde mediante el análisis del circuito en cada conmutación se definen los estados mostrados en la tabla 2.2.

Sustituyendo la variable  $S_1$  por S y usando los valores de la tabla 2.2, se obtiene

$$i_1 = Si, (2.8)$$

$$V_2 = -Sv. (2.9)$$

Las ecuaciones (2.8)–(2.9) representan una fuente de corriente dependiente y una fuente de voltaje dependiente, respectivamente. Usando las ecuaciones (2.8)–(2.9) se reconfigura el circuito del convertidor como se muestra en la figura 2.10.

Del circuito equivalente mostrado en la figura 2.10, se realiza el análisis mediante leves de Kirchoff. De este análisis, se obtienen ecuaciones que describen la dinámica de la

Figura 2.10: Circuito equivalente con fuentes dependientes del convertidor elevador.

corriente del inductor L y del voltaje del capacitor C, dadas por

$$\frac{di}{dt} = -\frac{1}{L}E - (1 - S)\frac{1}{L}v, \tag{2.10}$$

$$\frac{di}{dt} = -\frac{1}{L}E - (1 - S)\frac{1}{L}v,$$

$$\frac{dv}{dt} = (1 - S)\frac{1}{C}i - \frac{1}{RC}v.$$

(2.10)

Como se mencionó en secciones anteriores, este análisis es realizado asumiendo el modo de conducción continua, y el sistema en estado estable. Estas suposiciones definen el comportamiento del voltaje v(t) y la corriente i(t) como variables promediadas y los parámetros C y L como constantes, por lo que el modelo promediado finalmente queda representado de manera similar al modelo (2.10)-(2.11), pero renombrando la señal de control S como u(t), la cual es una función suave que toma valores en el intervalo [0,1].

Finalmente el modelo del convertidor reductor queda definido como

$$L\frac{di}{dt} = -(1-u)v + E, (2.12)$$

$$C\frac{dv}{dt} = (1-u)i - \frac{v}{R}. (2.13)$$

Para más referencias del modelo promediado consultar [3], [10], [58].

#### Definiciones de potencia y energía 2.4.

La potencia eléctrica se define como la proporción de energía entregada o recibida de un circuito a otro. Su unidad de medida es el Joule por segundo [J/s] aunque comúnmente se usa su equivalente, el Watt [W]. Su expresión matemática es definida como

$$p = \frac{dw}{dt},\tag{2.14}$$

donde p(t) es la potencia en Watts [W], w(t) es la energía en Joules [J] y t es el tiempo en segundos [s]. De manera general, la potencia eléctrica total p(t) puede escribirse como

$$p = vi$$

donde puede observarse que la potencia asociada a cualquier elemento de algún circuito es el producto del voltaje v(t) y la corriente i(t) a través de ese elemento [59].

Por otro lado, la energía se define como la capacidad para realizar un trabajo y su unidad es el joule [J] [60]. De la ecuación (2.14), la expresión de energía puede escribirse entonces como

$$dw = pdt$$

,

y en una ventana de tiempo entre  $t_0$  y t, la cantidad total de energía puede ser calculada como

$$w = \int_{t_0}^t p dt. \tag{2.15}$$

De manera práctica y comercial, la energía entregada en términos de consumo es expresada como kilowatt-hora [kWh]. Un kilowatt-hora es definido entonces como la potencia eléctrica de kW consumida en una hora, lo cual puede expresarse como

$$e = pT, (2.16)$$

donde e(t) es la energía eléctrica en kWh, p es la potencia eléctrica en kW y T es el tiempo en horas [59], [61].

# 2.4.1. La potencia y energía en un convertidor de C.D.-C.D. como factores para determinar las ganancias de un controlador

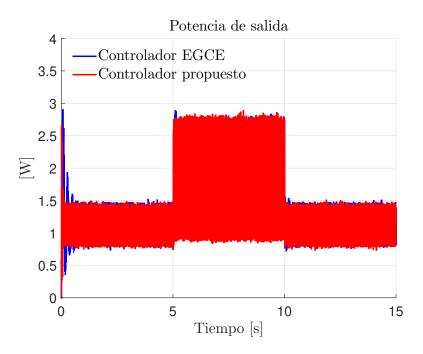

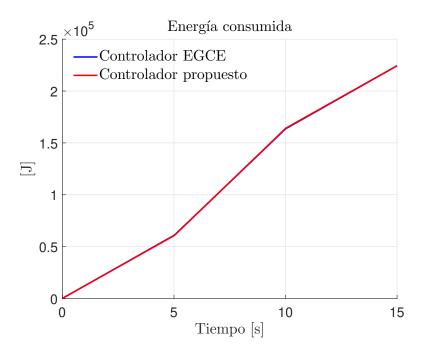

El presente trabajo propone esquemas de control para convertidores de potencia C.D.—C.D. que buscan cumplir la tarea de regulación. Para comprobar la eficiencia y desempeño de los controladores diseñados en este trabajo de tesis, se realiza una comparación con controladores existentes en la literatura diseñados para la misma tarea de regulación.

Para poder comprobar que esta comparación es justa, además de cubrir las tareas de control, se presenta de cada esquema controlador—convertidor, la potencia y energía correspondiente. Esto con la finalidad de determinar el desempeño de cada esquema y así poder comprobar que la elección de las ganancias es justa.

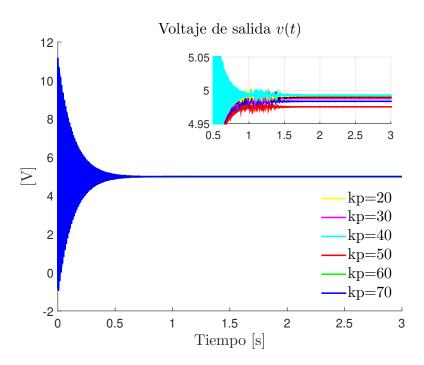

## Simulación de un controlador PI y un convertidor buck para medir los efectos de la potencia y la energía

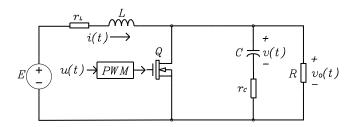

La siguiente simulación se realizó con un convertidor reductor (buck) usando los parámetros mostrados en la tabla 2.3.

| Símbolo | Valor | Unidad         |

|---------|-------|----------------|

| L       | 5     | [mH]           |

| C       | 1000  | $[\mu { m F}]$ |

| R       | 64.25 | $[\Omega]$     |

| E       | 10    | [V]            |

| $v_d$   | 9     | [V]            |

Tabla 2.3: Parámetros del convertidor buck.

Para el control del convertidor, se implementó un controlador proporcional—integral con retroalimentación de voltaje. La ganancia proporcional se sintonizó en el rango

$$20 \le k_p \le 70$$

,

y la ganancia integral se sintonizó en

$$k_i = 0.0001.$$

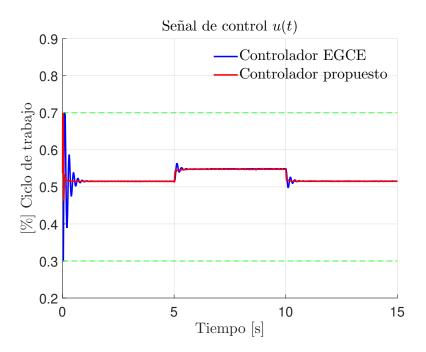

El propósito de variar la ganancia proporcional es observar el comportamiento del voltaje de salida, la señal de control, la potencia y la energía consumida en el convertidor reductor con el mismo controlador sintonizado diferente.

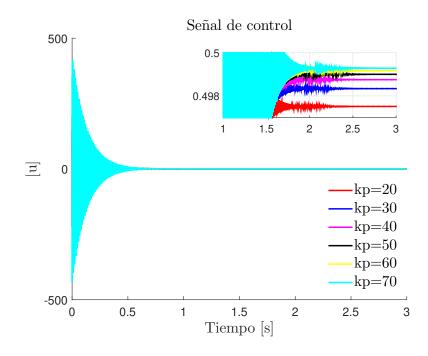

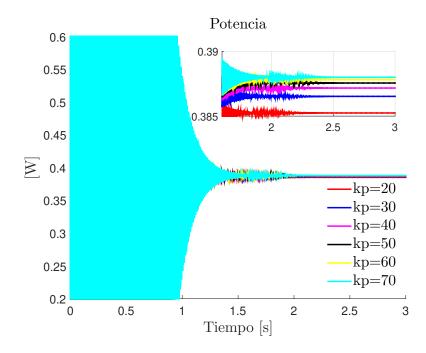

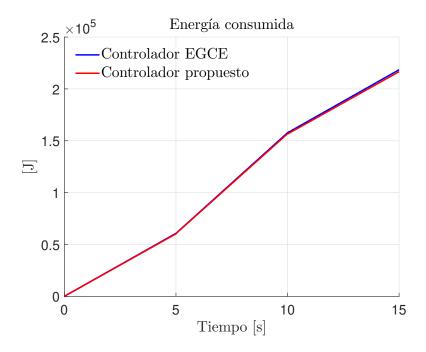

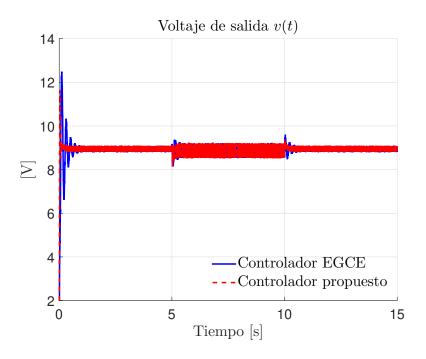

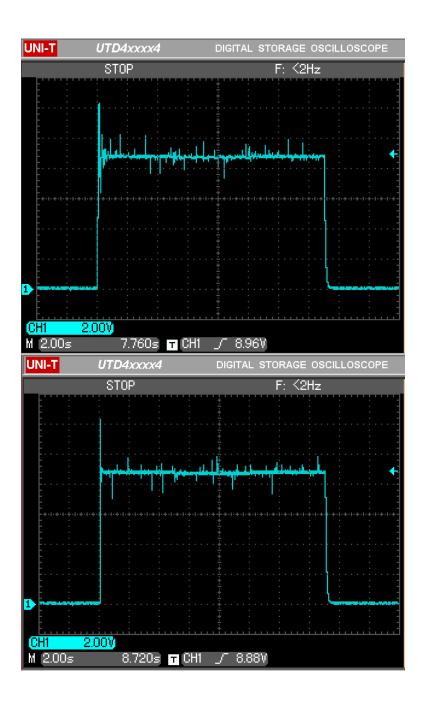

Como puede observarse en las figuras (2.11)–(2.13) los valores del voltaje de salida, señal de control y de la potencia de salida son muy similares en el rango de valores de la ganancia proporcional  $k_p$ , con variaciones de milésimas de unidades en los 3 casos.

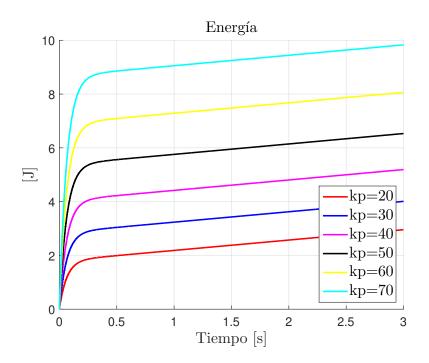

En cambio, los consumos de energía como pueden observarse en la figura (2.14) son muy diferentes entre si. Este comportamiento demuestra que a pesar de que el comportamiento de algunas variables como el voltaje de salida del convertidor y la misma potencia sean similares, el parámetro a observar al momento de comparar controladores, debe ser la energía.

El hecho de que la energía de salida sea similar pone en igualdad de circunstancias a los controladores evaluados, ya que no se exige a que alguno genere más ó menos energía y por lo tanto se acelere su tiempo de asentamiento y respuesta, lo cual es una forma de

Figura 2.11: Voltajes de salida del convertidor buck con control PI variando su ganancia kp.

poder validar la comparación de los esquemas de control en los experimentos.

Incluso si el objetivo de control es logrado en menor tiempo y con menos kWh (menos energía), implicaría una mejora adicional del controlador.

Este análisis puede extenderse para hablar de variables económicas que, en la práctica puede ser determinante para la elección de algún esquema controlador—convertidor específico tanto por su desempenño en campo, como por cuestiones energético—económicas.

Figura 2.12: Señal [u] del controlador PI variando su ganancia kp.

Figura 2.13: Potencia consumida del convertidor buck con control PI variando su ganancia kp.

Figura 2.14: Energía consumida del convertidor buck con control PI variando su ganancia kp.

## Capítulo 3

# Control de un convertidor boost con entrada restringida.

Comúnmente el voltaje de entrada necesario en muchos sistemas eléctricos y electrónicos es más grande que el voltaje de la fuente de entrada, por ejemplo, en sistemas alimentados por baterías. Una de las soluciones convencionales a este problema es el uso de un convertidor de potencia en su configuración elevadora comúnmente conocido como convertidor boost. Usualmente el porcentaje del ciclo de trabajo es la entrada del control del convertidor de potencia, el cual puede tomar los valores [0, 1) y sus restricciones son raramente tomadas en cuenta para el diseño del sistema de control. La razón es el aumento de la complejidad del análisis de estabilidad del sistema en lazo cerrado. Para poder proveer robustes y compensar variaciones desconocidas en la carga, en el voltaje de la fuente y disturbios no modelables, muchos algoritmos de control son diseñados para lograr regulación de voltaje a la salida del convertidor.

#### 3.1. Objetivos de control

- Tomar en cuenta los límites definidos del porcentaje del ciclo de trabajo en el diseño del controlador.

- Tomar en cuenta componentes parásitos para el diseño de un mejor controlador.

- Realizar regulación del voltaje de salida.

- Probar la convergencia asintótica del error de voltaje de salida a pesar de que el sistema está afectado por la saturación de entrada.

Figura 3.1: Circuito del convertidor boost con resistencias parásitas  $r_L$  y  $r_C$ .

#### 3.2. Contribuciones

- Se propuso un nuevo controlador para un convertidor de potencia boost con entrada restringida (saturada).

- Implementación de un observador para el voltaje de la fuente de entrada y la corriente de inductor.

- Validación de los resultados teóricos por medio de experimentos en tiempo real.

#### 3.3. Modelado del convertidor

El modelo usado es el correspondiente al circuito de la figura 3.1 el cual considera resistencias parásitas tanto en el inductor como en el capacitor. Esta última resistencia disipa el voltaje en la carga y descarga del capacitor. Los valores nominales de estas resistencias parásitas se asumen conocidas. El modelo matemático del sistema con resistencias parásitas es presentado en [21] y está dado por

$$L\frac{di}{dt} = -\left[r_L + [1-u]^2 \frac{r_C R}{r_C + R}\right] i - [1-u] \frac{R}{r_C + R} v + E, \tag{3.1}$$

$$C\frac{dv}{dt} = [1 - u]\frac{R}{r_C + R}i - \frac{1}{r_C + R}v,$$

(3.2)

donde u(t) es una señal de control continua que representa al porcentaje de ciclo de trabajo del circuito modulador que controla al MOSFET, E representa el voltaje de la fuente, i(t) representa la corriente a través del inductor L, v(t) es el voltaje a través del capacitor C y finalmente  $r_L$ ,  $r_C$  y R representan la resistencia del inductor, capacitor y de carga respectivamente.

El voltaje de salida está dado por

$$v_o = \frac{R}{r_C + R}v + [1 - u]\frac{r_C R}{r_C + R}i.$$

(3.3)

El punto de equilibrio del sistema descrito por las ecuaciones (3.1)-(3.2), asumiendo un porcentaje de ciclo de trabajo constante es

$$u(t) = 1 - D^*, (3.4)$$

el cual satisface

$$0 = -\left[r_L + D^{*2} \frac{r_C R}{r_C + R}\right] i_d - D^* \frac{R}{r_C + R} v_d + E, \tag{3.5}$$

$$0 = D^* \frac{R}{r_C + R} i_d - \frac{1}{r_C + R} v_d, \tag{3.6}$$

y que tienen como solución

$$i_d = \frac{v_d}{D^* R},$$

$$v_d = \frac{D^* RE}{r_L + D^{*2} R}.$$

(3.7)

Dado que  $v_d$  es un parámetro independiente, la ecuación (3.7) puede ser resuelta para  $D^*$ , que es el complemento del ciclo de trabajo. Por lo tanto

$$D^* = D_1^* \circ D_2^*,$$

donde

$$D_1^* = \frac{RE + \sqrt{[RE]^2 - 4Rv_d^2 r_L}}{2Rv_d}, \tag{3.8}$$

$$D_2^* = \frac{RE - \sqrt{[RE]^2 - 4Rv_d^2 r_L}}{2Rv_d}, \tag{3.9}$$

son las raíces de  $D^*$  y  $v_d$  es el voltaje de capacitor deseado. La solución utilizada  $D^* = D_1^*$  es la considerada en este trabajo. Una observación importante es que en el punto de operación  $i = i_d$  y  $v = v_d$ , donde el voltaje de salida  $v_o = v_d$ , lo cual puede ser confirmado a partir de la definición de  $v_o$  en la ecuación (3.3), por lo tanto,  $v_d$  indica el voltaje de salida deseado. En general, se puede decir que  $D^*$  es una función de la resistencia de carga

R, tensión de entrada E, la tensión deseada  $v_d$  y la resistencia del inductor R, es decir,

$$D^*(R, E, v_d, r_L).$$

En la práctica, el porcentaje de ciclo de trabajo u(t) debe satisfacer la restricción

$$0 < u(t) < 1, \ \forall \ t \ge 0, \tag{3.10}$$

por lo que el punto de equilibrio de la ecuación (3.4) también debe satisfacer

$$0 < 1 - D^*(R, E, v_d, r_L) < 1, (3.11)$$

esto significa que para parámetros fijos  $R, E, y r_L$ , el valor deseado  $v_d$  debe seleccionarse de tal manera que la ecuación (3.8) satisfaga la restricción (3.11), lo cual siempre está garantizada para

$$v_d > \frac{R}{R + r_L} E. \tag{3.12}$$

El objetivo de control consiste en la especificación de la salida deseada  $v_d$  que satisfaga la condición (3.12) y el diseño de una ley de control u(t) que satisfaga la restricción (3.10) tal que el voltaje de salida  $v_o(t)$  en la ecuación (3.3) logre que

$$\lim_{t \to \infty} v_o(t) = v_d,\tag{3.13}$$

mientras que la corriente del inductor i(t) y la tensión del condensador v(t) permanecen delimitadas para todo tiempo  $t \geq 0$ .

#### 3.4. Controlador propuesto

Primeramente se define la función de saturación como

$$sat(\bar{u}) = \begin{cases} u_{\text{máx}}, & \text{para } \bar{u} > u_{\text{máx}}, \\ \bar{u}, & \text{para } u_{\text{mín}} \leq \bar{u} \leq u_{\text{máx}}, \\ u_{\text{mín}}, & \text{para } \bar{u} < u_{\text{mín}}, \end{cases}$$

(3.14)

Dado que

$$0 < u_{\min} < D^* < u_{\max} \le 1$$

,

satisfecha, entonces

$$sat(D^*) = D^*.$$

El controlador propuesto está dado por

$$u = 1 - sat(D^* + \phi), \tag{3.15}$$

$$\dot{\phi} = \gamma [v_d e_i - i_d e_v] - \gamma k_{aw} [sat(D^* + \phi) - D^*],$$

(3.16)

donde  $\gamma$  y  $k_{aw}$  son constantes estrictamente positivas y  $\phi$  es una variable del controlador. Los errores quedan definidos como

$$e_i = i - i_d, (3.17)$$

$$e_v = v - v_d, (3.18)$$

los cuales denotan el error de corriente de inductor y el error de voltaje de capacitor, respectivamente. La definición de la función de saturación en la ecuación (3.14) permite garantizar que u(t) realmente satisface la ecuación (3.10), es decir,

$$1 - u_{\text{máx}} \le u(t) \le 1 - u_{\text{mín}},$$

de modo que

$$0 \le 1 - u_{\text{máx}} < D^* < 1 - u_{\text{mín}} < 1.$$

Ahora se define la función

$$\delta = \bar{u} - sat(\bar{u}),\tag{3.19}$$

en donde

$$\bar{u} = D^* + \phi, \tag{3.20}$$

y sustituyendo la acción de control dada en la ecuación (3.15) en las ecuaciones del convertidor boost (3.1)-(3.2), la dinámica del error se puede escribir como

$$L\frac{de_{i}}{dt} = \delta \frac{R}{r_{C} + R} v - [r_{L} + sat(u)^{2} \frac{r_{C}R}{r_{C} + R}] e_{i} - r_{L}i_{d} - sat(u)^{2} \frac{r_{c}R}{r_{C} + R} i_{d} + D^{*2} \frac{r_{C}R}{r_{C} + R} i_{d} - D^{*} \frac{r_{C}R}{r_{C} + R} i_{d} + E - [[D^{*} + \phi]e_{v} + v_{d}\phi + D^{*}v_{d}] \frac{R}{r_{C} + R},$$

(3.21)

$$C\frac{de_{v}}{dt} = -\delta \frac{R}{r_{C} + R} i - \frac{e_{v}}{r_{C} + R} - \frac{v_{d}}{r_{C} + R} + [D^{*} + \phi] \frac{R}{r_{C} + R} e_{i} + \phi \frac{R}{r_{C} + R} i_{d} + D^{*} \frac{R}{r_{C} + R} i_{d},$$

(3.22)

con  $\delta$  en la ecuación (3.19). Cabe señalar que

$$0 = -r_L - D^* \frac{r_C R}{r_C + R} i_d + E - D^* v_d \frac{R}{r_C + R}, \tag{3.23}$$

$$0 = D^* \frac{R}{r_C + R} i_d - \frac{v_d}{r_C + R}, \tag{3.24}$$

corresponden a las ecuaciones (3.1)–(3.2) del convertidor boost evaluado en el punto de operación  $i=i_d$ ,  $v=v_d$  y  $u=1-D^*$ . Usando las ecuaciones (3.23)–(3.24) en las ecuaciones (3.21)–(3.22), el sistema de lazo cerrado se puede escribir como

$$L\frac{de_{i}}{dt} = \delta \frac{R}{r_{C} + R} v - [r_{L} + sat(\bar{u})^{2} \frac{r_{C}R}{r_{C} + R}] e_{i} + [D^{*2} - sat(\bar{u})^{2}] \frac{r_{c}R}{r_{C} + R} i_{d} - [D^{*} + \phi] e_{v} \frac{R}{r_{C} + R} - v_{d} \phi \frac{R}{r_{C} + R},$$

(3.25)

$$C\frac{de_v}{dt} = [D^* + \phi] \frac{R}{r_C + R} e_i + \phi \frac{R}{r_C + R} i_d - \frac{e_v}{r_C + R} - \delta \frac{R}{r_C + R} i, \qquad (3.26)$$

$$\frac{d}{dt}\phi = \gamma[v_d e_i - i_d e_v] - \gamma k_{aw}[sat(D^* + \phi) - D^*]. \tag{3.27}$$

Es posible mostrar que el origen del espacio de estados, dado por

$$\begin{bmatrix} e_i \\ e_v \\ \phi \end{bmatrix} = \begin{bmatrix} 0 \\ 0 \\ 0 \end{bmatrix} \in \mathbb{R}^3,$$

es un punto de equilibrio del sistema de lazo cerrado (3.25)–(3.27).

Para demostrar la estabilidad global del origen de espacio de estados se propone la función candidata de Lyapunov:

$$W(e_i, e_v, \phi) = \frac{L}{2}e_i^2 + \frac{C}{2}e_v^2 + \gamma^{-1}\frac{R}{r_C + R}U(\phi),$$

(3.28)

con  $\gamma > 0$  y  $\mathcal{U}(\phi)$  definida por

$$\mathcal{U}(\phi) = \frac{\phi^2}{2} - \int_0^{\phi} \delta(\bar{u}) d\phi. \tag{3.29}$$

La función W en la ecuación (3.28) es definida positiva globalmente. Nótese que la función  $\mathcal{U}(\phi)$  es positiva definida. Después de manipulación algebráica se puede obtener el límite

superior de  $\dot{W}$ , el cual es dado por

$$\dot{\mathcal{W}} \le - \begin{bmatrix} |e_i| \\ |\phi - \delta| \end{bmatrix}^T Q \begin{bmatrix} |e_i| \\ |\phi - \delta| \end{bmatrix} - \frac{|e_v|^2}{r_C + R},\tag{3.30}$$

con

$$Q = \begin{bmatrix} r_L + u_{\min}^2 \frac{r_C R}{r_C + R} & -\frac{1}{2} [3D^* + u_{\max}] \frac{r_C R}{r_C + R} i_d \\ -\frac{1}{2} [3D^* + u_{\max}] \frac{r_C R}{r_C + R} i_d & k_{aw} \end{bmatrix}.$$

Debido a que la matriz Q es definida positiva, entonces (3.30) es globalmente negativa definida. Por lo tanto, existen condiciones suficientes para asegurar que el origen del espacio del sistema de lazo cerrado dado en las ecuaciones (3.25)-(3.27) es estable globalmente y uniformemente asintótico, véase como ejemplo [62], [63], lo cual también implica que

$$\lim_{t \to \infty} \begin{bmatrix} e_i(t) \\ e_v(t) \\ \phi(t) \end{bmatrix} = \begin{bmatrix} 0 \\ 0 \\ 0 \end{bmatrix}, \tag{3.31}$$

para toda condición inicial  $[e_i(0) \ e_v(0) \ \phi(0)]^T \in \mathbb{R}^3$ .

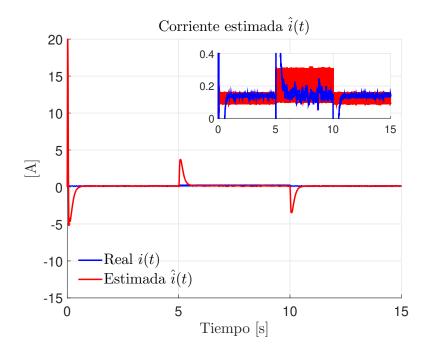

## 3.4.1. Controlador propuesto para voltaje de entrada y corriente de inductor desconocidos

El controlador propuesto dado en las ecuaciones (3.15)–(3.16) asume que todos los parámetros son conocidos, lo cual en la práctica esto no siempre es posible. Para agregar robustes a las propiedades del controlador se propone uno nuevo considerando  $\hat{E}(t)$  y  $\hat{i}(t)$ , como estimaciones del voltaje de entrada E y de la corriente de inductor i(t). Se propone el nuevo controlador dado en las ecuaciones (3.15)–(3.16) escrito en términos de las señales  $\hat{E}(t)$  y  $\hat{i}(t)$  dado por

$$u = 1 - sat(\hat{D}^* + \phi),$$

(3.32)

$$\dot{\phi} = \gamma [v_d[\hat{i} - i_d^*] - i_d^* e_v] - \gamma k_{aw} [sat(\hat{D}^* + \phi) - \hat{D}^*], \tag{3.33}$$

donde

$$\hat{D}^* = \hat{D}_1^* = \frac{R\hat{E} + \sqrt{[R\hat{E}]^2 - 4Rv_d^2 r_L}}{2Rv_d},$$

e

$$i_d^* = \frac{v_d^2}{\hat{E}R},$$

son el complemento del porcentaje de ciclo de trabajo estimado y la corriente estimada deseada, respectivamente. Para evitar la singularidad, se asume que  $\hat{E}(t) > 0$  y  $[R\hat{E}(t)]^2 - 4Rv_d^2r_L > 0$  para todo  $t \ge 0$ . Se define la variable

$$\boldsymbol{z} = \begin{bmatrix} \tilde{E} \\ \tilde{i} \end{bmatrix} = \begin{bmatrix} \hat{E} \\ \hat{i} \end{bmatrix} - \begin{bmatrix} E \\ i \end{bmatrix}, \tag{3.34}$$

la cual denota el error de observación. Tomando en cuenta el trabajo de Karagiannis [23], el cual es nombrado en este trabajo como controlador KAO, se realizó una implementación experimental para comparación con el controlador propuesto. Este controlador [23] resuelve el problema de robustes en la regulación de voltaje para un convertidor boost con parámetros parciales e información de los estados, el cual está dado por

$$u = 1 - sat\left(\frac{\hat{E}}{v_d}\right),\tag{3.35}$$

donde la entrada de control y el observador son

$$\frac{d}{dt}\eta_{1} = -\frac{\lambda_{1}}{C}[[\eta_{2} + \lambda_{2}v][1 - u] - \frac{1}{R}v], \qquad (3.36)$$

$$\frac{d}{dt}\eta_{2} = -\frac{\lambda_{2}}{C}[[\eta_{2} + \lambda_{2}v][1 - u] - \frac{1}{R}v]$$

$$+\frac{1}{L}[\eta_{1} + \lambda_{1}v - v[1 - u]], \qquad (3.37)$$

con constantes  $\lambda_1, \lambda_2 > 0$  y salidas definidas por

$$\hat{E}(t) = \eta_1(t) + \lambda_1 v(t), \tag{3.38}$$

У

$$\hat{i}(t) = \eta_2(t) + \lambda_2 v(t). \tag{3.39}$$

Las señales dadas en las ecuaciones (3.38) y (3.39) indican la estimación del voltaje de la fuente el cual es usado en la entrada de control dada en la ecuación (3.35), y la corriente de inductor estimada, respectivamente.

Mediante el uso de las ecuaciones (3.1)–(3.2) del convertidor boost en con  $r_L$  y  $r_C$

iguales a cero, la definición de z en la ecuación (3.34) y las ecuaciones (3.36)–(3.39) del observador, es posible mostrar que

$$\frac{d}{dt} \begin{bmatrix} z_1 \\ z_2 \end{bmatrix} = \begin{bmatrix} -\frac{\lambda_1}{C} [1-u] z_2 \\ \frac{1}{L} z_1 - \frac{\lambda_2}{C} [1-u] z_2 \end{bmatrix}, \tag{3.40}$$

la cual tiene un punto de equilibrio z = 0 que es asintóticamente estable.

Motivados por el trabajo presentado en [23], se propone el siguiente controlador usando las ecuaciones (3.15)–(3.16) las cuales, como se ha explicado anteriormente, toman en cuenta las resistencias parásitas del inductor y capacitor

$$u = 1 - sat(\hat{D}^* + \phi), \tag{3.41}$$

$$\dot{\phi} = \gamma [v_d[\hat{i} - i_d^*] - i_d^* e_v] - \gamma k_{aw} [sat(\hat{D}^* + \phi) - \hat{D}^*], \tag{3.42}$$

donde

$\hat{D}^* = \hat{D}_1^* = \frac{R\hat{E} + \sqrt{[R\hat{E}]^2 - 4Rv_d^2 r_L}}{2Rv_d},$

e

$$i_d^* = \frac{v_d^2}{\hat{E}B}.$$

Inspirados en el observador propuesto en [23], se propone el siguiente observador

$$\frac{d}{dt}\eta_{1} = -\frac{\lambda_{1}}{C} \left[ [1 - u] \frac{R}{r_{C} + R} \hat{i} - \frac{1}{r_{C} + R} v \right],$$

$$\frac{d}{dt}\eta_{2} = -\frac{\lambda_{2}}{C} \left[ [1 - u] \frac{R}{r_{C} + R} \hat{i} - \frac{1}{r_{C} + R} v \right]$$

$$+ \frac{1}{L} \left[ -[1 - u] \frac{R}{r_{C} + R} v + \hat{E} - r\hat{i} \right],$$

(3.43)

con

$$r = r_L + [1 - u]^2 \frac{r_C R}{r_C + R},$$

y constantes  $\lambda_1, \lambda_2 > 0$ . Además,

$$\hat{E}(t) = \eta_1(t) + \lambda_1 v(t), \tag{3.45}$$

У

$$\hat{i}(t) = \eta_2(t) + \lambda_2 v(t).$$

(3.46)

#### 3.4.2. Corolario

Controlador propuesto

$$u = 1 - sat(\hat{D}^* + \phi),$$

$$\dot{\phi} = \gamma [v_d[\hat{i} - i_d^*] - i_d^* e_v] - \gamma k_{aw} [sat(\hat{D}^* + \phi) - \hat{D}^*],$$

con límites de saturación

$$0 \le 1 - u_{\text{máx}} < \hat{D}^* < 1 - u_{\text{mín}} < 1,$$

donde

$$\hat{D}^* = \hat{D}_1^* = \frac{R\hat{E} + \sqrt{[R\hat{E}]^2 - 4Rv_d^2 r_L}}{2Rv_d},$$

$$i_d^* = \frac{v_d^2}{\hat{E}R}, v_d > 0,$$

y ganancias

$$\gamma, k_{aw} > 0,$$

con el observador

$$\begin{split} \frac{d}{dt}\eta_1 &= -\frac{\lambda_1}{C} \left[ [1-u] \frac{R}{r_C + R} \hat{i} - \frac{1}{r_C + R} v \right], \\ \frac{d}{dt}\eta_2 &= -\frac{\lambda_2}{C} \left[ [1-u] \frac{R}{r_C + R} \hat{i} - \frac{1}{r_C + R} v \right] + \frac{1}{L} \left[ -[1-u] \frac{R}{r_C + R} v + \hat{E} - r \hat{i} \right], \end{split}$$

donde

$$r = r_L + [1 - u]^2 \frac{r_C R}{r_C + R},$$

y ganancias  $\lambda_1, \lambda_2 > 0$ . Además,

$$\hat{E}(t) = \eta_1(t) + \lambda_1 v(t),$$

у

$$\hat{i}(t) = \eta_2(t) + \lambda_2 v(t).$$

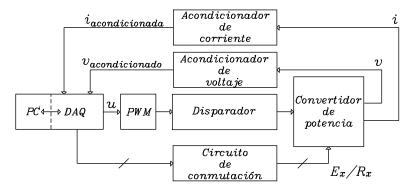

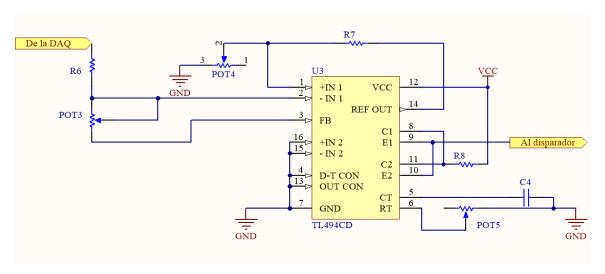

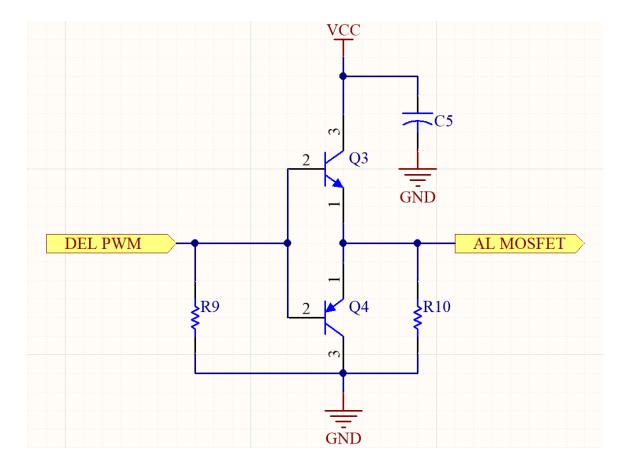

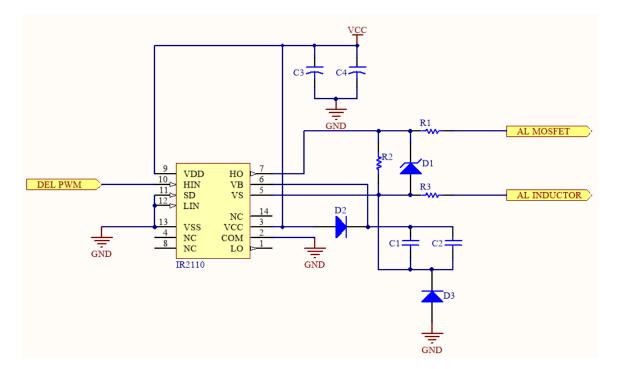

#### 3.5. Resultados experimentales

Los resultados experimentales del control propuesto y el controlador KAO son presentados a continuación. La dinámica del error de observación está dada por

$$\frac{d}{dt} \begin{bmatrix} z_1 \\ z_2 \end{bmatrix} = \begin{bmatrix} -\frac{\lambda_1}{C} [1 - u] \frac{R}{r_C + R} z_2 \\ \frac{1}{L} z_1 - \frac{r}{L} z_2 - \frac{\lambda_2}{C} [1 - u] \frac{R}{r_C + R} z_2 \end{bmatrix}, \tag{3.47}$$

la cual es obtenida de las ecuaciones (3.1)–(3.2) del convertidor boost en, el vector z en la ecuación (3.34) y las ecuaciones (3.1)–(3.2) del observador. Puede observarse que el origen del espacio de estados del sistema (3.47) es exponencialmente estable.

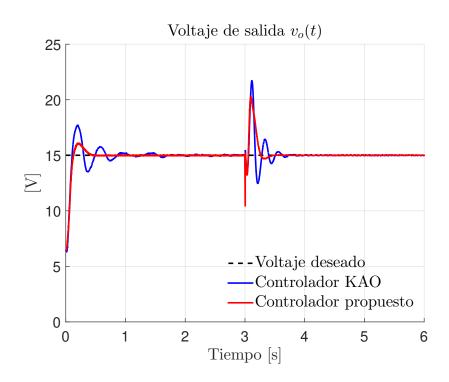

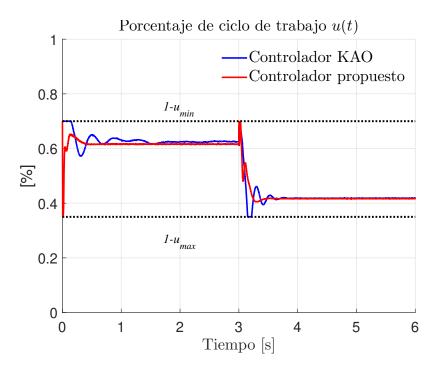

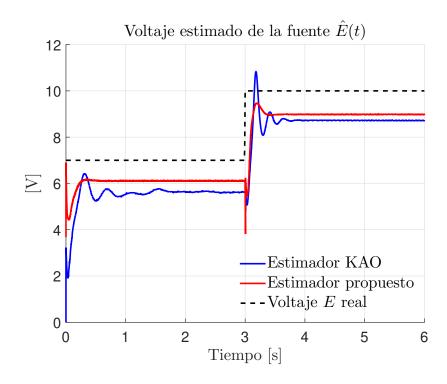

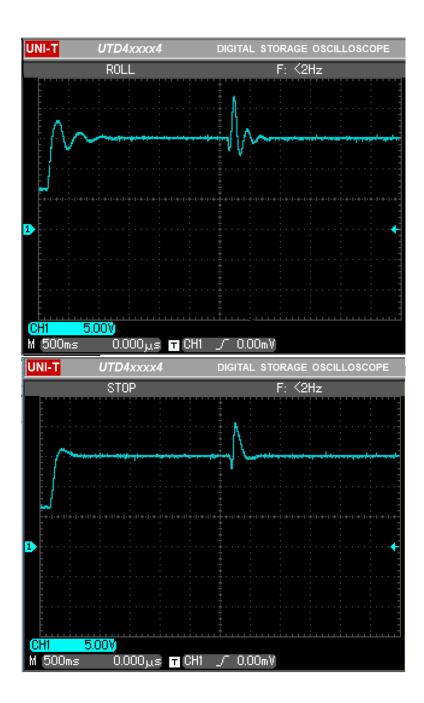

Los experimentos fueron realizados en la plataforma experimental donde los límites de saturación están dados por

$$1 - u_{\text{máx}} = 0.35 \le u(t) \le 0.7 = 1 - u_{\text{mín}}$$

y el voltaje de la fuente del convertidor boost es variado de la forma

$$E(t) = \begin{cases} 7 \text{ [V]}, & \text{para } 0 \le t < 3, \\ 10 \text{ [V]}, & \text{para } 3 \le t < 6. \end{cases}$$

Las ganancias usadas en los observadores (3.36)–(3.37) y (3.43)–(3.44) en todos los experimentos fueron  $\lambda_1 = 0.5$  y  $\lambda_1 = 0.1$ .

El nuevo controlador dado en las ecuaciones (3.41)–(3.41) fue implementado con  $\phi(0) = 0$  y ganancias

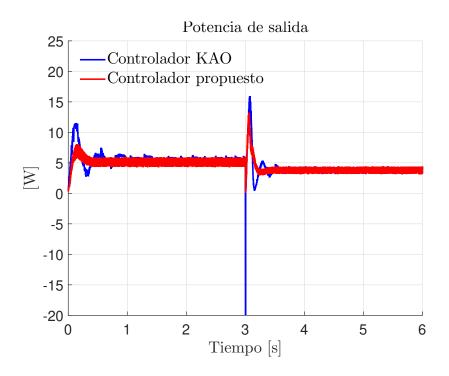

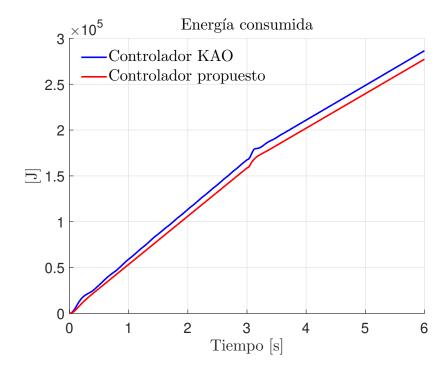

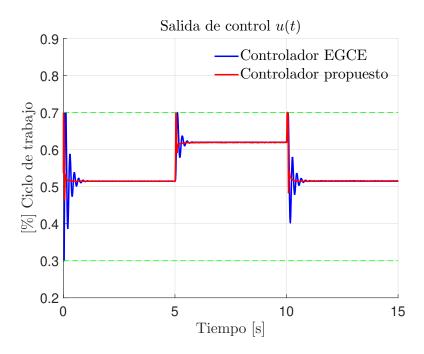

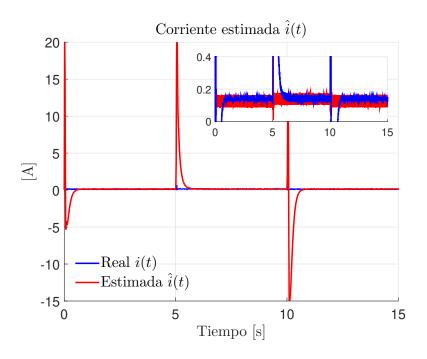

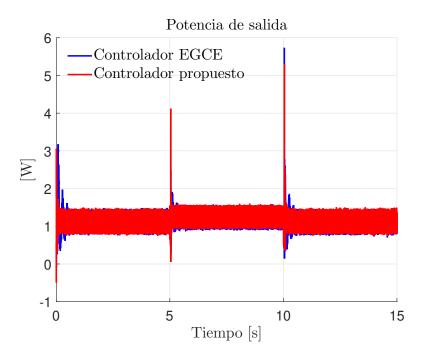

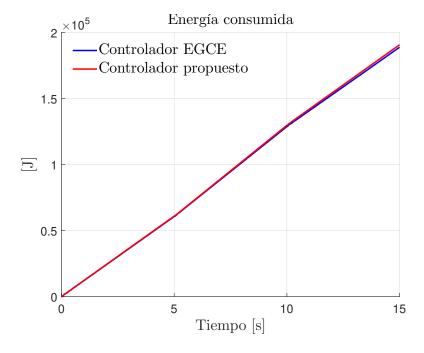

$$\gamma = 10, \ y \ k_{aw} = 10.$$